今回から半導体プロセスの話をしていこう。まずこれに先立って、2013年11月にインテルが開催した投資家向け説明会の資料をもとに、インテルの14nm以降のプロセスと、これにまつわるビジネスの話を解説していこう。

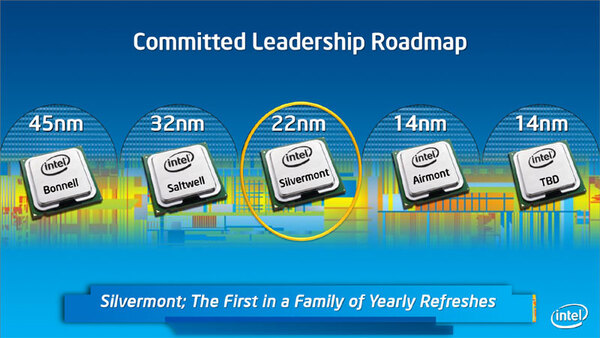

Atomのロードマップ。次期プロセッサーは14nmプロセスで製造される

量産が約3ヵ月遅れる

14nmプロセスの動向

元々昨年10月に行なわれた2013年第3四半期の決算報告の中で、同社CEOであるBrian Krzanich氏が14nmプロセスの量産開始を1四半期遅らせることを発表している。

本来だと2013年末にはこの14nmプロセスを使っての製造が開始されるはずだったため、これが2014年3月あたりまで伸びる計算だ。ということは、14nmプロセスを利用して製造した製品がファウンダリーから出てくるのは早くて5月末、実際には6月に入ってからになると思われる。

この14nmの遅れに関しての詳細が、同社のWilliam Holt氏(Exective Vice President&General Manager, Technology and Manufactureing Group)から説明があった。

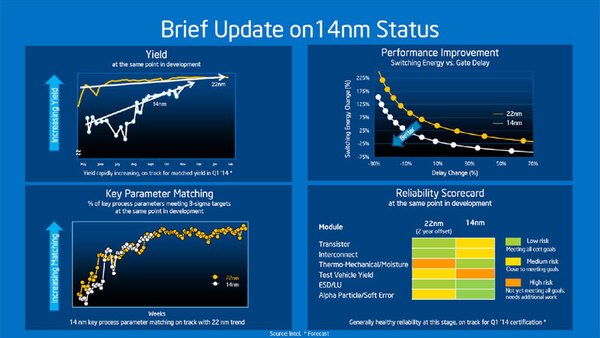

14nmの状況を22nmの場合と比較したものが上の写真である。画像は縮小してあり見づらいので、右上を除く3つについてそれぞれ大きく示していこう。

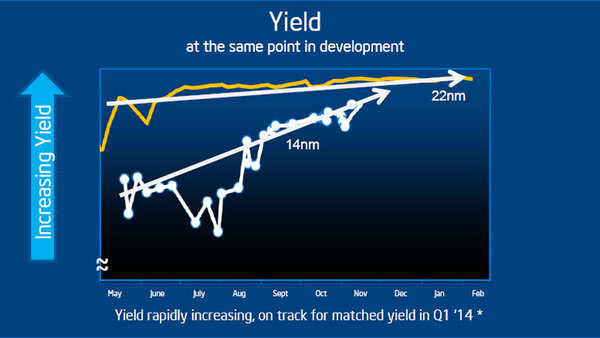

下の画像は、歩留まり(Yield)の比較である。22nmについては、現在ではなく2年前の状態を基にした結果であるが、これと比較すると14nmはやや立ち上がりがもたついていることがわかる。

インテルの推定によれば2014年1月には22nmと同等の歩留まりが達成できるという見込みであるが、実際には2013年の6~8月はずいぶん苦しんだ様子が伺えるし、10月も色々大変だったようで、このまま推定どおり2014年1月中に22nmと同等の歩留まりが達成できるのか、もう少し情報がほしいところだ。

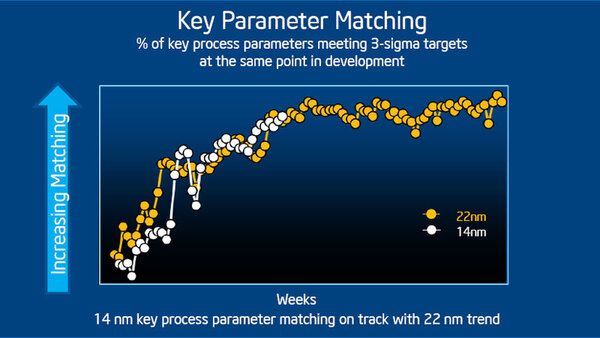

下の画像は22nmプロセスと14nmプロセスの両方を使って製造したウェハーの物理的な特徴を比較したものである。例えばある電圧・温度である電圧をかけたときに電流はどうなるか、その際の遅れはどの程度かなどの目標パラメーターが、どんなプロセスでも設計段階で決められており、その数は数百から数千ある。

プロセスの開発段階では試しに流したウェハーについて、こうしたパラメーターを全部測定し、目標にあった結果が出ているかどうかを確認するわけだが、上の画像はこの合い方を示したものである。14nmプロセスのパラメーター改善は、22nmの時とほぼ同じ具合に進んでいるとしている。

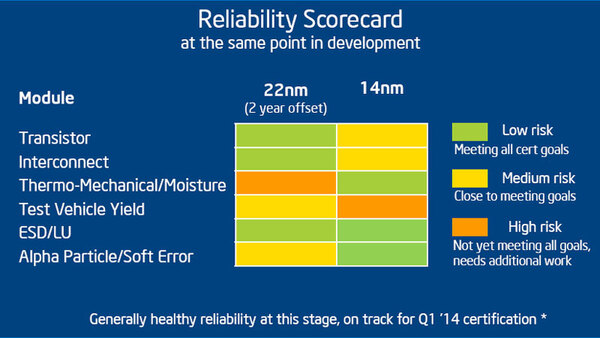

最後が信頼性に関するもので、22nmはやはり2年前の状況を示したものである。以下のように、ほぼ22nmと同等レベルが達成できている、としている。

- トランジスターおよび内部配線の信頼性:22nmはほとんど問題なかったが、14nmではまだいくつか改善の必要あり

- 熱・機械的信頼性及び湿度対策:22nmでは深刻な問題であったが、14nmではほぼ問題なし

- テスト用ビークルの信頼性:22nmではやや改善の必要がある程度だったが、14nmでは大分改善の必要あり

- 静電気放電/ラッチアップに関する信頼性:22nm/14nmともにほぼ問題なし

インテルはこれまで、未発表のプロセスの詳細をここまで公開することはなかった。もちろんIEDM(IEEE International Electron Devices Meeting:半導体素子に関する国際学会)に、研究レベルでの発表を行なうことは煩雑にあったが、量産プロセスに関しては完成後に報告というのがほとんどだった。

それが今回前倒しで14nmプロセスの動向を説明したのは、後述するファウンダリーサービスへの配慮であろうと考えられる。そのファウンダリーサービスの話は後回しにして、まずは性能の話をしよう。

消費電力が下がり性能が向上する

プロセスの微細化はいいことづくめ

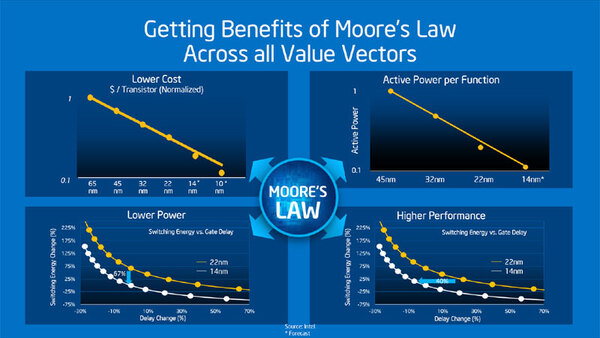

下の画像が全体をまとめたものだが、トランジスターコストは着実に下がり、機能あたりの消費電力も下がり、かつ性能は向上することが示されている。左上はトランジスター1個あたりのコストを、65nm世代を1とした場合に換算したもの。

縦軸は対数なので、14nm世代で0.2位になる。右上は機能(例えば1個のゲート)あたりの消費電力で、これは45nm世代を1とすると、14nm世代では0.1近くまで落ちる。

下の2つのグラフは、22nm世代と14nm世代を比較した場合、動作周波数が同じなら動的消費電力が67%減少(左下)、動的消費電力が同じなら速度が40%向上(右下)としている。

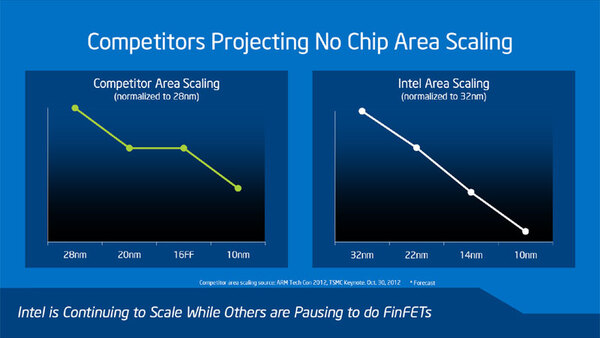

またダイ面積を比較した場合、TSMCなどの競合は20nm世代と16nm/14nm世代で密度を上げられないのに対し、インテルは継続して密度を上げられる、と主張している。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ