プロセスの基礎知識そのものはまだ山ほどあるのだが、前回までで最低限必要な要素は解説したので、今回から実際の半導体プロセスの説明に入っていく。

シリコンウェハー

半導体プロセスの基本

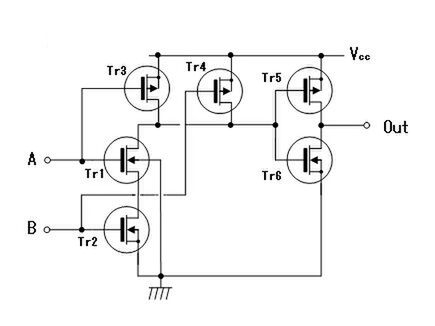

前回、デジタル半導体は基本的な組み合わせ回路のみで作りこめると説明した。では実際にデジタル半導体がどうやって製造されるか、というのが今回のテーマである。図1は前回も紹介したAND回路の構図である。これをシリコン上にどうやって構築するか解説していこう。

図1 AND回路の構図。作図の都合上、Tr4の向きを逆にしたが、動作そのものは変わらない

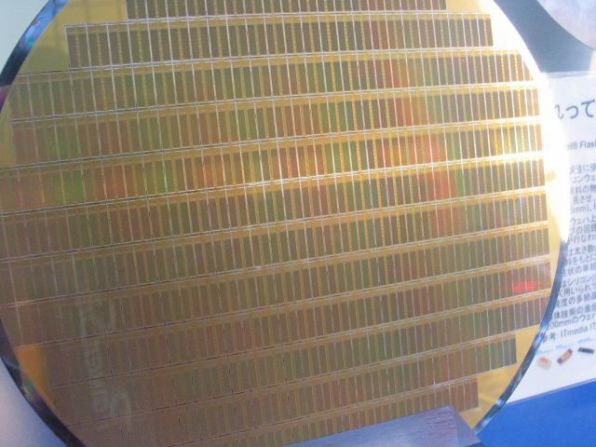

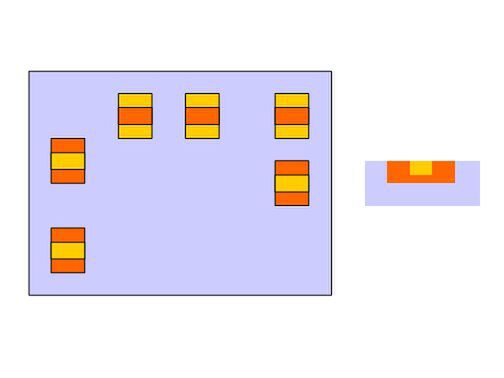

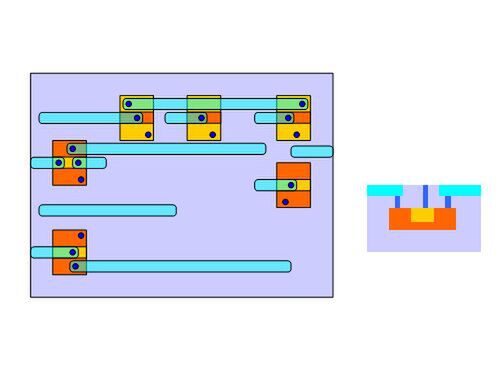

まず最初にシリコンウェハーの上に、トランジスタを構築する。図2はウェハーの上にトランジスタを構築した様子を示したもので、左側は上から、右側は横からこれを見たものと考えてほしい。

図2 ウェハーの上にトランジスタを構築した様子

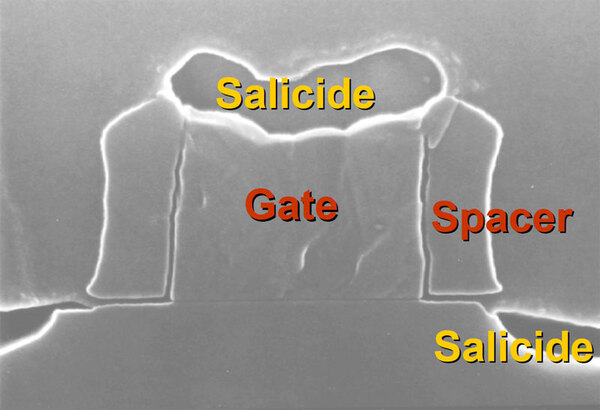

ちなみに図2では断面図を綺麗に描いたが、実際は下の写真のような感じである。

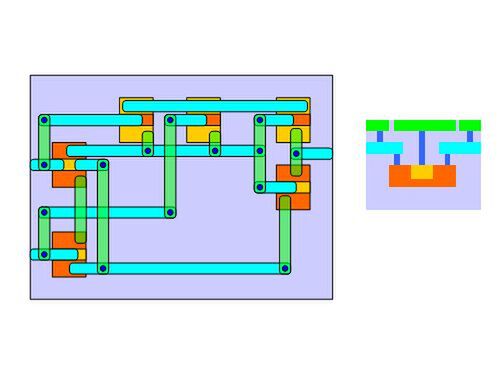

さて、トランジスタができたら、次にそれをつなぐ必要がある。図1のケースでは、いくつか配線が交差している箇所があるので、これを平面配線にするのは非常に難しい。したがって配線は必然的に立体配線となる。

立体配線にも色々あるが、一般的なのは縦横方向の配線を重ねる方法である。まずトランジスタの端子部にVIA(貫通端子)を立て(図3の青い丸の部分)、次いでその上に配線(図3左側で水色の部分)を重ねる。空いている部分は絶縁体で埋める形だ。

図3 トランジスタ同士を配線でつなぐ。まずは横方向の配線(水色の横線)を行なう

これができたら、次に縦方向の配線を同じように行なう(図4)。これで配線が完了というわけだ。

図4 横方向の配線の上に縦方向の配線(緑色の縦線)を重ねる

実際には配線層が2層だけでは大規模回路では到底間に合わない。特にSoCなどでは、長距離の配線や内部バスも必要であって、局所的な配線のために2~4層、大きな配線にもやはり2~4層の配線を重ねることになる。

またここには入れていないが、実際には電源/GNDの配線にそれぞれ1層づつ、さらにクロック信号の分配に2層程度が必要になるため、最近のSoCは10層前後もの配線層が重なっている。ちなみに筆者が知ってる範囲で一番大きなものは13層にもおよぶ。

最近のものでは連載235回で示したインテル製SoCの断面写真(下の写真)を見てもらえればわかりやすい。この断面写真で一番下がトランジスタで、残りは全部配線層になる。

駆け足で解説してきたが、この最初の「トランジスタを構築する」だけで数十工程が必要である。まず最初にやることは、ベースとなるシリコンウェハーの製造だ。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ