AMDのロードマップアップデートが終わったので、再び先端プロセスの話に戻ろう。今回は、非常に広くその技術が知られており、かつ効果があることもわかっているにも関わらず、製品への採用例が皆無という「Body Bias」について説明したい。

微細化の天敵であるリーク電流を抑える

Body Bias

Body Biasは、連載246回で少しだけ触れたが、ゲート・リーク電流を抑えるのに有効な方法である。今回はその詳細を解説しよう。下図は、連載236回で説明したMOSFETの構造の概略である。今回のテーマはこのゲートである。

MOSFETの構造。説明の都合上、連載236回で示した図の上下をひっくり返している

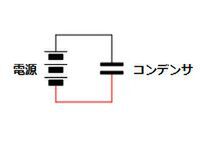

ゲート電圧をかけると、この電圧に応じてドレイン電流が流れるというのがMOSFETの仕組みである。要するに酸化膜がコンデンサーの働きをしてくれるわけで、ゲートから見た等価回路は下図のようになる。

ゲートから見た等価回路

この図で赤く描いた部分が、実は最初の図からは抜けている。いや単に省いただけなのだが、これを描き入れると下図のようになる。つまり、ゲートからかけた電圧は、そのままGNDに落とされているわけだ。これが、ここまで説明してきた一般的な構造である。

ゲートからかけた電圧は、そのままGNDに落とされる

Body Biasはゲート電圧をGNDに落とさずに、下図のように端子を引っ張り出し、ここにも電圧をかける仕組みだ。これにより、トランジスタのスレッショルド電圧が変化したり、トランジスタの特性が変化するという傾向が広く知られている。

Body Biasの仕組み。BIAS端子を引っ張り出し電圧をかける

具体的には、BIAS端子に順電圧、つまりマイナスの電圧をかけるとトランジスタはより高速に、もしくはより消費電力を減らせる一方で、ゲート・リーク電流が増えてしまうことが知られている。逆に逆電圧(プラスの電圧)をかけると、トランジスタそのものの速度が落ちる一方で、ゲート・リーク電流が減るようになる。リーク電流の度合いは、当然ながら電圧によって変化する。

これを利用することで、トランジスタの特性を揃えたり、リーク電流を減らしたりできるというのがBody Biasの骨子である。例えばインテルはMITと共同で、2002年11月に論文(PDF)を発表している。論文は、回路の一部を細かく分割して異なるBIAS電圧を与えることで、特性がどう変化するかをまとめて報告したものだ。

論文によれば以下の結果が得られている。

- 450mVのFBBを掛ける(Forward Body Bias:要するにBIAS電圧に-450mVを掛ける)と、BIAS電圧が0の時に比べて消費電力を23%削減できる

- 450mVのRBBを掛ける(Reverse Body Bias:逆電圧で、BIAS電圧に450mVを掛ける)と、BIAS電圧が0の時に比べてスタンバイ時のリーク電流を7分の2に削減できる

これをもっと積極的に活用しよう、というのが「Adaptive Body Bias」と呼ばれる技法である。これは、トランジスタが動いているときは順電圧を、動いていないときは逆電圧をかけるようにすれば、動作周波数を引き上げつつ、消費電力を減らせて万々歳というわけである。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ