前回はDRAMの近未来展望を説明したので、今回はフラッシュメモリーについて説明しよう。すでにおなじみSSDのコアとなるコンポーネントだ。

半導体プロセスの話でフラッシュメモリーの説明をするのは、DRAMよりもシビアな、以下のような状態になっているからだ。

- DRAMにも増して容量増加の要求が高く、これに向けてDRAMよりもさらに微細化を進めることになった。

- 微細化だけでは足りないので多値化もやった。

- それでも足りずに3Dに向けてすでに量産に入った。

さて、フラッシュメモリーの構造も説明してなかったので、まずはここから始めたい。フラッシュメモリーと一口に言っても、大別してNOR型とNAND型がある。実はどちらも発明者は一緒で、東芝の元社員、舛岡富士雄氏によるものだ。

最初に発明されたのがNOR型で、次いでNAND型が発明された。もっともNOR型とNAND型は、基本的な記憶素子の構造は同一で、配線が異なるのみである。もっともその配線の違いにより以下の違いがある。

- NAND:高集積化に向いており、書き込みは相対的に高速。ただしアクセスはブロック単位で、ランダムアクセスは低速

- NOR:集積度は低くなるが、バイト単位でのアクセスが可能。書き込みは遅いが、ランダムアクセスは高速

ただ、どちらにせよ原理そのものは一緒ということで、ここからはNANDフラッシュをもうすこし細かく説明していく。セルの構造そのものについて言えば、最初に発明されたのがフローティング・ゲートで、次いでチャージ・トラップという構造が2006年に開発されている。

ほかにもSpansionが特許を持っているミラー・ビットという構造もあるが、あまり一般的ではないのでここでは割愛する。

NANDフラッシュがデータを保持する仕組み

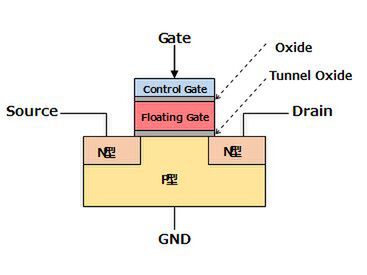

図1がそのフラッシュメモリーのセルの基本構造である。通常のNMOSによく似た構造であるが、異なるのはゲートが二重構造になっていること。まずP型半導体と接する部分にトンネル酸化膜と呼ばれる薄い絶縁構造があり、その上にFloating Gate(浮遊ゲート)と呼ばれる部分がある。さらにその上に絶縁膜を挟んでゲートが構築されるという構造である。

図1 フラッシュメモリーの基本構造

フラッシュメモリーの基本的な動作は、このフローティング・ゲートと呼ばれる箇所に電荷を蓄えることで、記憶素子とする仕組みである。具体的にはどんな形で動作するかということで、まずは記憶を保持する場合だ。

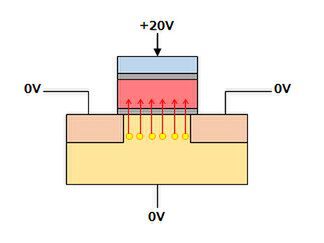

コントロール・ゲートにのみ+20V程度をかけ、あとを全部0Vにすると、電子がトンネル酸化膜を貫通して、フローティング・ゲートに流れ込む(図2)。

図2 記憶を保持する場合は、コントロール・ゲートにのみ電圧をかけ、電子をフローティング・ゲートに流し込む

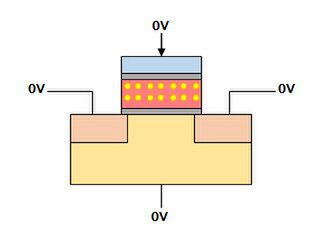

ある程度流れ込んだ状態でコントロール・ゲートの電圧も0にすると、フローティング・ゲートに流れ込んだ電子はそのまま行き場をなくした状態で保持されることになる。これが、値として“0”を保持した状態である(図3)。

図3 コントロール・ゲートの電圧を0にすると、フローティング・ゲートに流れ込んだ電子はそのまま行き場をなくした状態で保持される

逆に消去はどうするかというと、図2とは逆に、コントロール・ゲート以外に20Vをかけることで、フローティング・ゲートに保持されていた電子がトンネル酸化膜を貫通して流れ出し、フローティング・ゲートの中に電子が残らなくなる。この状態が、値として“1”になるわけだ(図4)。

図4 消去の場合は、コントロール・ゲート以外に電圧をかけることで、フローティング・ゲートに保持されていた電子を流し出す

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ