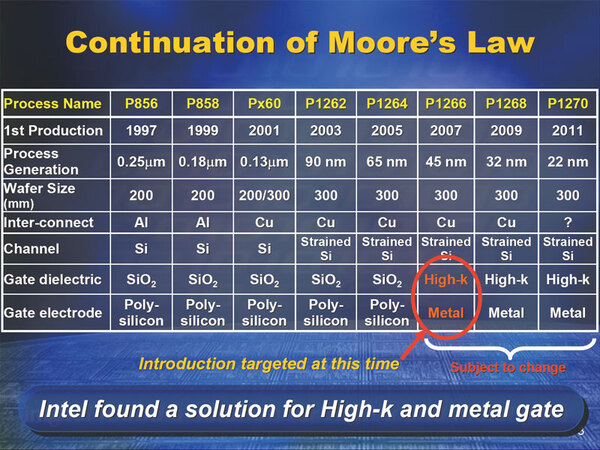

前回はゲート絶縁膜を薄くしすぎてゲート・リーク電流がすさまじいこと解説した。リーク電流の解決のために導入されたのがHKMG(High-K Metal Gate)と呼ばれる材料である。それについて、引き続きインテルの資料を使いながら順を追って説明したい。

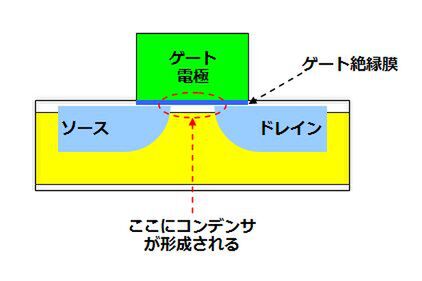

そもそもなぜゲート絶縁膜を薄くする必要があるのかをおさらいしよう。図1はインテルのプレゼンテーションにならった形でトランジスタの構造を描いたものだ。

トランジスタの構造

MOSFETの場合はゲート電極とシリコンの間に絶縁膜を設けると、ここが事実上コンデンサーを形成することになり、このコンデンサーの蓄電/放電でスイッチのOn/Offが行なわれることになる。コンデンサーの容量が大きいほど、スイッチングのOn/Offが高速化する。というわけで、うまくコンデンサーの容量を増やしてやればよい。ところが以下のジレンマに陥っていた。

- 容量を大きくするには面積を増やせばよいが、幅(=Gate Length)はプロセスの微細化に従う形になるので、大型化どころか小型化の一途を辿っており、こちらは期待できない。

- 厚みを減らした結果、ゲートリークが発生してしまっており、むしろ増やしたい。

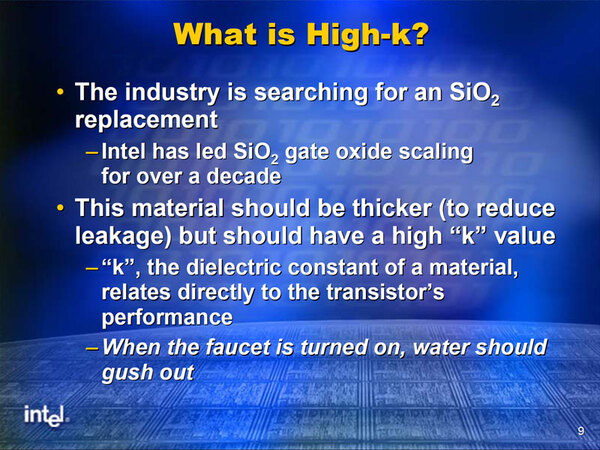

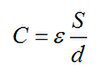

そこで、「ゲート絶縁膜の厚みを増しながら、コンデンサーの容量を増やす」ための方法論を業界は古くから模索していた。ここで出てくるのが比誘電率というファクターである。やや電磁気学のお勉強になるが、コンデンサーの静電容量Cは以下のように示される。

Sは電極板の面積(図1ではゲート電極やチャネルの面積)、dは電極板の距離(図1ではゲート酸化膜の厚さ)である。コンデンサーの容量を増やすには、面積を増やすか距離を縮めるしかないが、どちらも無理というのは前回説明した通り。

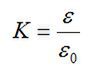

そこで目を付けたのが誘電率のεである。εそのものは物質毎に固有の値であるが、通常は絶対値ではなく、ε0(真空の誘電比)との比率であるKを使って表現する。

つまり、距離を大きく、面積を小さくしても、比誘電率が高い物質をゲート絶縁膜に使えば、コンデンサーの容量が大きくなるというわけだ。このK、シリコン酸化膜の場合で大体2.9前後といわれている。ガラスで5~9、水が20度の場合に80.9、チタン酸バリウムは5000で、このあたりは本当に物質によってまちまちである。

ただ半導体プロセスに使う以上、CMOSの製造プロセスと親和性のある材料でないと使うのは難しい。半導体業界はこのKが40前後という、比誘電率が高い物質(High-K)を長年捜し求めてきた。

インテルがHigh-K材料を決定

ゲート・リーク電流を100倍以上削減

さて、話をインテルのプレゼンテーションに戻そう。2003年11月にインテルが発表したのは、このHigh-K材料を決めたとともに、それを使った製造プロセスにめどが立ったことをアナウンスしたものである。

次のスライドの説明は、まさに今ここまで書いてきたような内容がまとめられているが、10年以上も時間がかかったのにはそれなりに理由がある。もともとHigh-K材料は、半導体プロセスでコンデンサーを利用する、例えばDRAMなどの分野で広く求められていた。

比較的早期から利用されてきたのは酸化チタン(TiO2)で、最初に発表されたのは1969年までさかのぼる。もっともこれは量産ではなくあくまで研究レベルの話である。

2003年にはSTMicroelectronicsがTa2O5(五酸化タンタル)をTiN(窒化チタン)膜で囲ったMIM(Metal-Insulator-Metal)構造のコンデンサーをDRAM向けに発表している。ただ五酸化タンタルはKが27前後で、インテルなどが求めているものよりもやや低かった。最終的にはHf(ハフニウム)をベースとした合金で、求めているKを満たすことができたとしている。

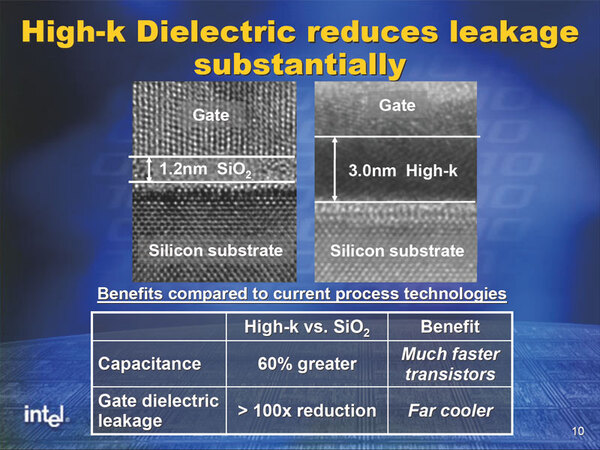

その結果として45nm世代では、ゲート酸化膜の厚みを3nmまで増すことが可能になった。この状態でコンデンサの容量は60%アップになり、それでいながらゲート・リーク電流を100倍以上削減することに成功している。

※お詫びと訂正:記事初出時「ゲート絶縁膜の厚みを増しながら、コンデンサーの容量を減らす」とありましたが、正しくは「コンデンサーの容量を“増やす”」になります。記事を訂正してお詫びします。(2014年4月12日)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 - この連載の一覧へ