前回はNTRS(National Technology Roadmap for Semiconductors)のロードマップに業界があわせる方向で舵を切ったあたりまでを解説した。引き続き、このロードマップの話をしていきたい。

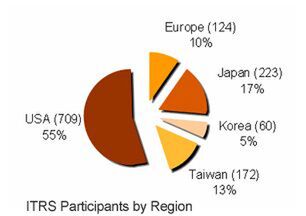

NTRSはその後、ITRS(International Technology Roadmap for Semiconductors)と名称を変え、アメリカだけでなく他の国の半導体メーカーや関連機器メーカーの意向も取り込んだものとなる。

形としては、アメリカのベンダーはSIAが引き続き取りまとめを行ない、これ以外に欧州のEECA(European Electronics Component Manufacturers Association)、韓国のKSIA(Korea Semiconductor Industry Association)、日本のJEITA(Japan Electronics and Information Technology Industries Association)、台湾のTSIA(Taiwan Semiconductor Industry Association)という組織もこのロードマップ策定に関係するようになった。

ITRSの参加国。ITRSのウェブサイトより抜粋

最初のバージョンは1999年版となり、以後奇数年(1999,2001,2003,...)はロードマップを発行、偶数年(2000,2002,...)はそのロードマップのアップデートを発行するスタイルとなる。このロードマップ、2000年のアップデートから後に関してはすべてオンラインで公開されている(関連リンク)。このロードマップに示されたプロセス進化の変遷について、概要を説明しよう。

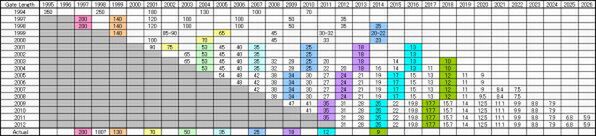

上の表は、それぞれのロードマップに示された、年度とプロセスノード、およびゲート長の関係である。どう読むかというと例えばプロセスノードの表では、1行目は1994年におけるロードマップで、1998年には250nmに、2001年には180nmに、2004年には130nmにそれぞれ移行すると予測している。

次の行は1997年における予測で、250nmが1997年、180nmが199年、130nmが2003年にそれぞれ実現すると予測されている。180nm以降が全部前倒しになっているわけだ。実際この1997年の予測で、130nmまでは2年ごとに新プロセスノードに移行することになっている。

表における一番下の行の“Actual”というのは、インテルがこのプロセスノードをいつごろ実現したかを示している。

まずはプロセスノードを見てみたい。180nmあたりはそれほど大きな違いはないが、130nmは当初から4年ほど前倒しとなっており、これは90nmなども同じである。この90nmまではITRSのロードマップとインテルのプロセスが合致しているが、この先は完全にずれることになる。

65nmは2007年に実現するが、インテルはこれを2005年に実現、45nmは2010年に実現の予定だったが、インテルは3年前倒しをする。22nmもそうだし、14nmもこれに近い。32nm世代から先に関しては、インテル以外のベンダーが急速に追い上げた関係で、もうロードマップとかなりかけ離れた状況になっているのだが、それはいずれ説明する。ただ、結果として以下の構図が読み取れると思う。

- ITRSは主要なプロセスノードの更新を3年ごとに想定して動かさない

- インテルは前倒しでこれを2年ごとに更新した

もう1つプロセスノードでわかるのは、2002年あたりから細かいプロセスノードが追加されたことだ。例えば2年なり3年ごとにプロセスノードは更新されていくとしても、その間ずっと同じプロセスを使っているのはあまりに進歩がないので、もう少し細かくプロセスを改善していきたい、ということである。

最終的に、これはハーフノードという形でまとまることになる。プロセスノードと比較すると以下の具合になっている。

| プロセスノード | 180nm → 130nm → 90nm → 65nm → 45nm → 32nm→ 22nm |

|---|---|

| ハーフノード | 150nm → 110nm → 80nm → 55nm → 40nm → 28nm → 20nm |

要するにプロセスノードの間をちょうど埋めるように、その中間の寸法のプロセスを挟み込むことで、連続的にプロセスを改善していこうという動きである。

寸法そのものは10~20%ほどの縮小だから、回路密度は20~40%程度の向上にしかならないが、仮に10%であってもトランジスタ数を増やしたり、あるいは省電力化/速度改善が実現できればそれだけでも差別化の要因になる。やや古い話だが、1998年にインテルが投入したP856.5プロセスのMendocinoコアはこの良い実例だった。

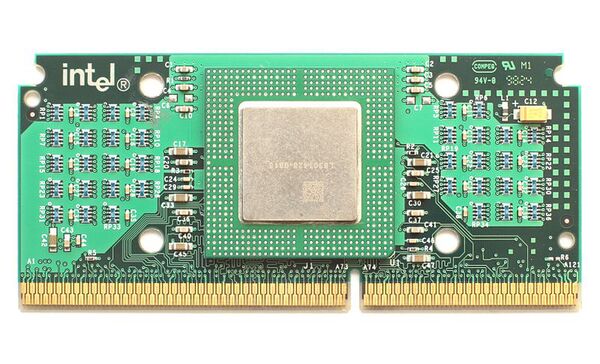

元々インテルはP856(0.25μm)プロセスを使ってDeschutesコアの「Pentium II」を製造した。このコアは750万トランジスタを131mm2のダイサイズに納めていた。Deschutesコアは2次キャッシュを持っておらず、外付けで最大512KBのPBSRAMを2次キャッシュとして接続する構成になっていたが、これは2次キャッシュをオンダイにしようとするとダイサイズが肥大化しすぎて歩留まりが一気に悪化するからであった。

ところがこれは当然高コストとなるので、小売価格を高く維持できるPentium IIはともかく、低価格向けのCeleronでは無理がある。そこであっさり2次キャッシュを省いた形で構成したのが第1世代のCovingtonというCeleronである。

ところがあまりに性能が悪すぎて評判が恐ろしく悪く、Celeronであってもやはり2次キャッシュは必要という結論に達した。ただ、外付け2次キャッシュはコストの面でCeleronには適さない。そこで0.25μmのハーフノードにあたる0.22μmプロセスを開発、これを使ったMendocinoコアのCeleronを投入した。

厳密に言えばこの0.22μmプロセスは、Dixonと呼ばれるMobile Pentium II向けのものである。モバイル向けだと外付け2次キャッシュは実装面積の観点で不適当であり、だからといって2次キャッシュを搭載しないと性能が低すぎる。そこで256KBの2次キャッシュをオンダイで搭載させたのがDixonであり、このDixonの2次キャッシュを半分殺して128KBにしたのがMendocinoである。

256KBの2次キャッシュともなると、それだけで1千万トランジスタほど追加が必要になる。結果Dixonコアは1890万ものトランジスタ数に膨れ上がる。これを0.25μmのまま製造したら、180mm2近いダイサイズになるところだが、P856.5を使うことでダイサイズを154mm2に押さえ込むことに成功した*1。

※1:キャッシュに使われるSRAMはCPUのロジック部よりもより高い密度で実装ができるので、トランジスタ数の比よりも面積の増分は抑えられる。

こうした前例があるからこそ、インテル以外のベンダーは通常のプロセスノードに加えてハーフノードもサポートするケースが多かった。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ