90nm世代のプロセス「P1262」を採用したPrescott。非常に難産だった

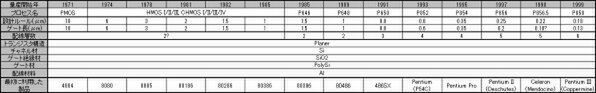

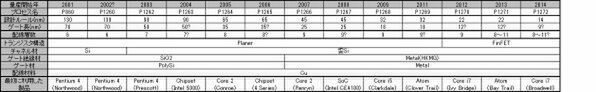

各社のロードマップ アップデートを挟んだため1ヵ月ほど間が空いてしまったが、再びプロセッサーのプロセスについて解説していく。今回は2003年にインテルが導入した90nm世代の「P1262」の話である。

銅汚染問題の次は

リーク電流対策

配線を銅に切り替えたことで高速化の障害が1つ減ったものの、相変わらずトランジスタの高速化は難しく、よりゲート長を短縮する必要があったのだが、これにあわせてもう1つ懸念事項が出てきていることは業界でも広く知られていた。それがリーク電流だ。

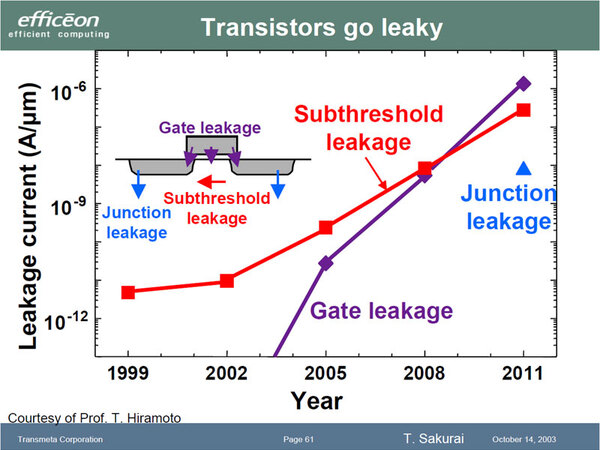

上のグラフは東京大学の桜井貴康教授が2003年10月に示したものだが、トランジスタが動作する際には、リーク電流と呼ばれるものが一定量発生する。蛇口をきっちり閉めても、ほんのわずかながら水が漏れるようなものだ。

大きな水栓ならあまり問題にならないが、水栓というかパッキングが小さくなると、どうしてもわずかに漏れることは避けられない。同様にトランジスタも、小型化によってあちこちから電流が漏れ出てくる。このリーク電流には3種類ある。

- 意図せずにドレインからソースに漏れてしまう、サブスレッショルド・リーク電流(Subthreshold Leakage)

- ゲートから漏れてしまうゲート・リーク電流(Gate Leakage)

- Drain/Sourceの電極から直接漏れてしまう、ジャンクション・リーク電流(Junktion Leakage)

グラフからもわかる通り、これまでリークといえばサブスレッショルド・リーク電流が主であった。このグラフ、縦軸が対数になっていることが肝である。

例えば2005年に予定されているトランジスタであれば、ゲート・リーク電流はサブスレッショルド・リーク電流の10分の1でしかないが、2008年頃にはこれが同等になり、2011年には10倍になると予測しているわけだ。実際には、ゲート・リーク電流はこの予測より早期に問題になってきている。

Transmetaはこの対策として一種のBody Biasを利用した「LongRun 2」という技術を開発し、NECやSONY、富士通/東芝/NVIDIAなどにライセンスを供給するものの、結局自社のプロセッサー「Efficeon」はLongRun 2を実装しないまま会社が終了してしまった。

最近ではSuVOLTAというメーカーが、やはりこのBody Biasを利用した「DDC(Deeply Depleted Channel)」なる技術を開発、いくつかのベンダーにこれをライセンス供与している。

話を戻すと、このゲート・リーク電流はトランジスタの性能との相反関係にある。なぜゲートから電流が漏れるのか。それはゲートの厚みが薄いためだ。したがってゲート・リーク電流を減らすにはゲートの厚みを増せばいい。

ところがゲートを厚くすると、スイッチングの速度が遅くなる。トランジスタを高速化するためには、ゲートは薄い方が有利なのである。2003年頃は、どのくらいの厚みでバランスを取るか、各社頭を悩ませていた時期でもある。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ