前回掲載したインテルの14nmプロセスの記事が予想外に反響があって驚いている。プロセスの話は今回からが本番。先端プロセスの話も後々出てくるが、その前に少し基本的なことのおさらいをしておきたい。

トランジスタベースのデジタル回路

電子回路には、アナログ回路とデジタル回路の2種類がある。両者の違いは、デジタル量で処理するか、アナログ量で処理するかである。デジタル量というのは0か1しかない。対してアナログ量は、連続した可変量を扱うことになる。

このデジタル量は、ブール代数と呼ばれる記号論理学を使って扱われることが多いが、今回はその話は後送りする。回路上で見ると、0~5Vの範囲で変動する電圧を持つ回路の場合、アナログ量だと0~5Vの範囲を連続する値として扱うのに対し、デジタル量ではどこかにしきい値を設けて、例えば2.5V以上ならそれを「1」、2.5V未満ならそれを「0」と扱う形になる※1。

※1:これは比喩であって、これでは2.5V付近で電圧がぐらついた時に値が0と1の間で激しく振動することになり、あまりよろしくない。実際は例えば1.5V以下を0、3.5V以上を1として、1.5~3.5Vの間は「不定」という扱いにする。

そのデジタル量を扱う部品がトランジスタである。トランジスタは1947年にアメリカのベル研究所で初めて半導体が発明されて以来、非常に広く利用されている。では、トランジスタはなにをするかというと、基本原理は「電流の増幅作用」である。

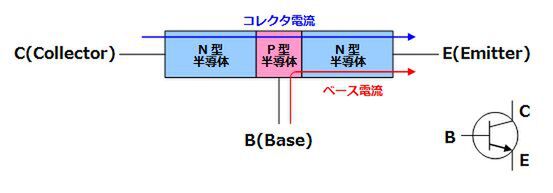

下の画像は非常にラフなトランジスタの模式図である。これはN型の半導体でP型の半導体をサンドイッチ構造にした、NPNタイプと呼ばれるものだ。

NPNタイプのトランジスタ模式図

NPNタイプは、「B(Base)からE(Emitter)に電流(ベース電流)を流すと、これに比例した電流(コレクター電流)がC(Collector)からEに流れる」という働きになる。図の右下が、このトランジスタを示す記号である。ちなみに図のN型半導体とP型半導体を逆にしたPNP型のトランジスタもある。

コレクター電流の大きさは、ベース電流の数十倍~数百倍にすることが可能で、「少ない電流で大電流を制御できる」という意味でこれを増幅作用と呼んでいる。

これがどうデジタル回路に関係してくるかというと、トランジスタを電流On/Offのスイッチとして使えるのである。つまり1ならスイッチOn(コレクター電流が流れる)、0ならOff(コレクター電流が流れない)といった実装になる。これを組み合わせてゆくことで、複雑なデジタル回路を構成してゆくというわけだ。

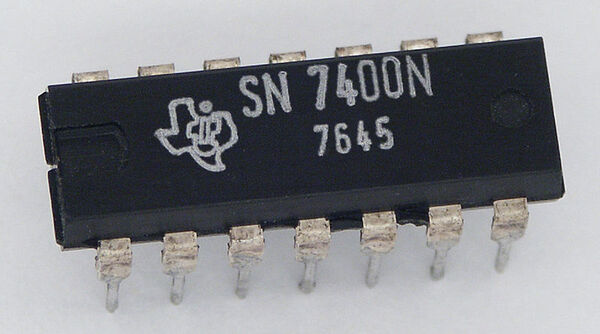

初期のデジタル回路やIC/LSIは全部この構成で実装されており、かつてはTTL(Transistor-Transistor Logic)と呼ばれるものが一般的だった。信号電圧は5Vで、TI(Texas Instruments)社が発売した7400シリーズは安価に入手できるTTL ICということで広く利用されていた。筆者も高校生の時分に作ったエレキーはTTL ICで構成した覚えがある。

このTTL ICにどのようなものがあったかは、英語で恐縮だがWikipediaの「List of 7400 series integrated circuits」(関連リンク)を見ていただいた方が早いだろう。

パッケージそのものは14~20ピン程度のプラスチックDIPパッケージで、ユニバーサル基板にDIPソケット経由などで簡単に配線できるうえ、ICそのものもそう高くなく、ウン十年前の高校生のポケットマネーで何とか買える程度だった。

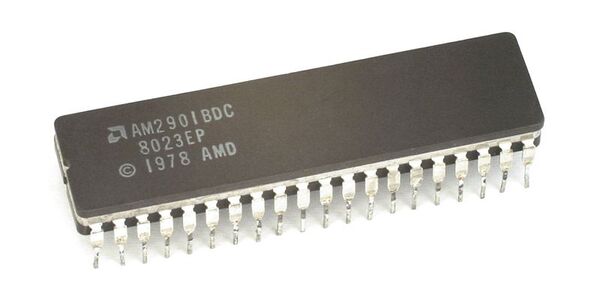

初期のコンピューターの中には、本当にこのTTL ICを使って構成されていたものも少なくない。連載122回でAMDのRISCプロセッサー「Am2900」のご先祖様にあたる「Am2900」シリーズに触れたが、このAm2900シリーズは内部はともかく外部はTTLレベルで信号が出ていた。したがって、Am2900を使ってCPUボードを作る場合、周辺回路は必然的にTTL ICを使うことになった。

さらには、TTL ICを使ってCPUを作るという優雅な趣味もあり、「CPUの創りかた」という書籍がマイナビから刊行されている。現実問題として使い物になるかどうかはともかく、技術的にはまだTTL ICでもデジタル回路が構成できる。

■Amazon.co.jpで購入

-

CPUの創りかた渡波 郁(著)毎日コミュニケーションズ

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ