NMOS単体に比べて低消費電力

かつ抵抗が必要ないCMOS

先にFETにはN型とP型があると記したが、MOSFETにも同様にNMOS(N型MOSFET)と、半導体の位置を入れ替えたPMOS(P型MOSFET)がある。このNMOSとPMOSは、動きがちょうど逆になる。

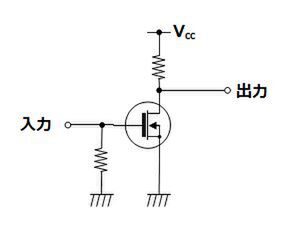

そこで、NMOSとPMOSを組み合わせることで、状態が変化しても電流が全く流れないようにできる。こう書いてもわかりにくいと思うので、実例を示そう。下図はNMOS単体で構成したインバーター(NOT回路)である。

NMOS単体で構成したインバーター

これは入力が1なら出力が0、入力が0なら出力が1となる。このケースだと、入力が0の場合、Vccからの電流はそのまま出力側に流れるので、NMOSは何も電力を消費しない。

ところが入力が1だと、Vccからの電力が抵抗を経て全部NMOS経由でGNDに流れてしまうので、ここで相応の消費電力が発生してしまう。これをカバーするために、NMOSとPMOSを組み合わせたインバーターが下図である。

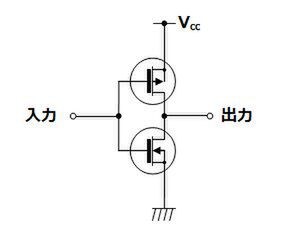

NMOSとPMOSを組み合わせたインバーター

上側がPMOS、下側がNMOSで構成されるが、入力が1のときPMOS側はドレイン全閉になるため、Vccからの電流はシャットダウンされる。一方NMOS側がドレイン全開になるため、出力はGNDと接続される=0と同等になる。

逆に入力が0だと、PMOS側はドレイン全開になるためVccがそのまま出力に流れることになる。その一方でNMOS側はドレイン全閉になるのでGNDと切り離されるわけで、無駄に電流を消費せずにすむ。つまり、NMOS単体に見られるような「無駄な消費電力」を減らせるのがCMOSというわけだ。

もちろんCMOSもまるで電力がかからないわけではない。入力が0→1、あるいは1→0に切り替わるとき、MOSFETそのものの状態が変化する際に若干の消費電力が費やされる。ただこれは、NMOS単体の抵抗で消費される電力に比べると桁違いに小さいもので、結果非常に省電力に貢献できたというわけだ。

もう1つメリットを挙げておくと、ICで大規模回路を構成する場合、抵抗を内蔵するのは難しい。ところがCMOSだと抵抗が必要ない(NMOS/PMOSを作るだけでいける)というのもメリットとされる。もちろんデメリットも色々あるわけだが、そのあたりは次回以降で説明しよう。

※お詫びと訂正:回路名の一部に誤りがありました。記事を訂正してお詫びします。(2021年2月11日)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ