久しぶりにAMD製CPUの話ということで、今回はISSCC 2025で説明されたZen 5コアの詳細を紹介していこう。Zen 5コアは、概略がCOMPUTEX TAIPEI 2024のレポート記事で触れられており、EPYCの周りの話は連載794回で説明している。ISSCCということもあり、物理実装や回路構成に関する、これまで説明がなかった内容も含まれていたので、それを説明する。

3種類の派生型があるZen 5

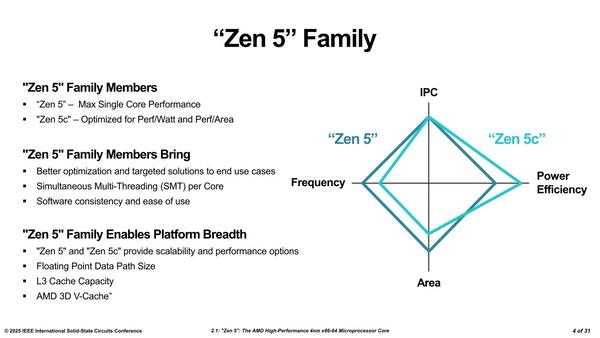

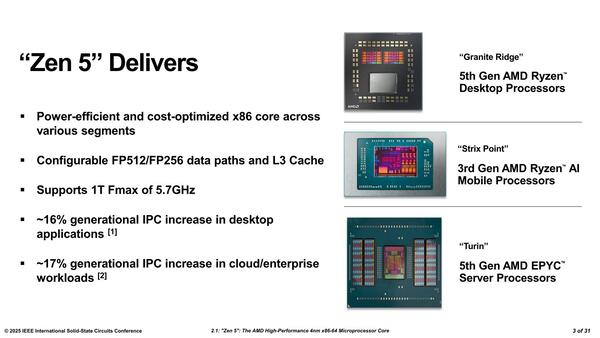

Zen 5世代は現時点で3種類の派生型がある。製品という意味ではデスクトップ向けのGranite Ridgeとモバイル向けのStrix Point、それとサーバー向けのEPYCの3種類ではあるのだが、まず物理実装でZen 5とZen 5cの差がある。

アーキテクチャーはZen 5と同じだが物理実装がZen 5とZen 5c、それとZen 5+Zen 5cのHybridの3種類ということになる。Granite RidgeがZen 5、TurinはZen 5ないしZen 5c、そしてStrix PointがHybridである

これはZen 4とZen 4cと同じで、論理的な構造は(L3のサイズを除くと)まったく同一である。異なるのは物理実装で、Zen 5が高速向けのCellライブラリーを利用しており、Zen 5cが省電力/高密度向けのCellライブラリーを利用しているという違いだ。

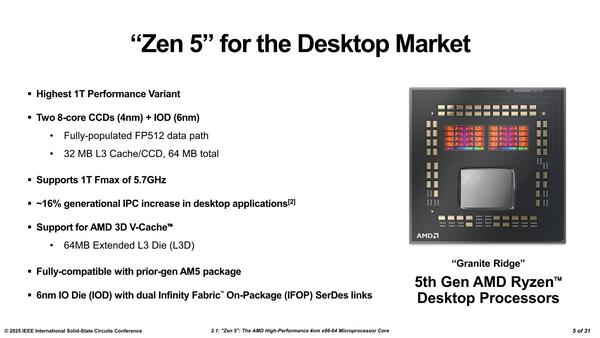

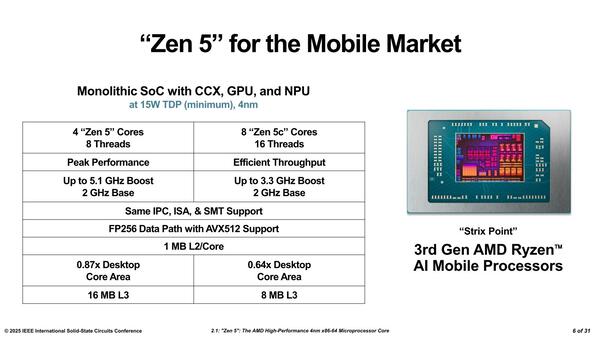

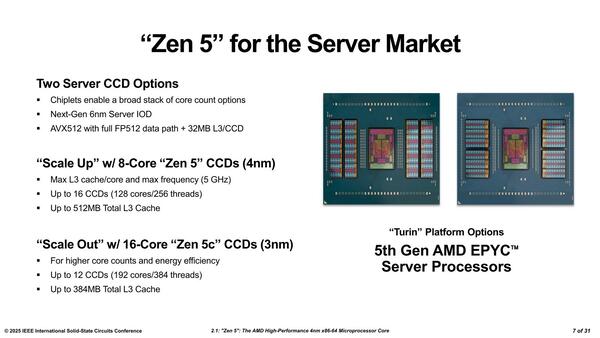

製品としてはGranite Ridgeが1ないし2つのZen 5 CCDと6nmのIODの組み合わせ、Strix Pointは4×Zen 5+8×Zen 5cをモノリシックとしたもの、TurinではGanite Ridgeと同じZen 5 CCDないし、(今のところは)Turin専用のZen 5c CCDを、新しく用意された6nm IoDと組み合わせる構成となっている。

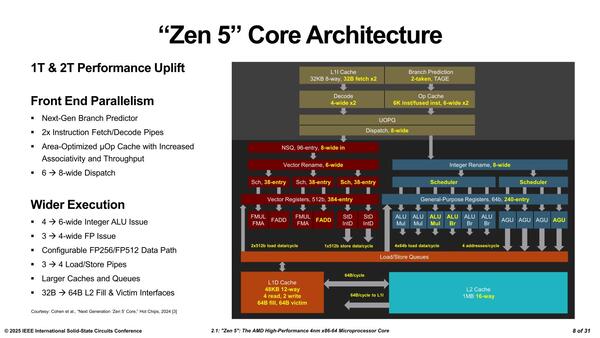

そのZen 5とZen 5cのCPUコアのブロック図が下の画像だ。このあたりまでの情報はすでに公開されている話である。

※お詫びと訂正:Strix Pointの説明に一部誤りがございました。記事を訂正してお詫びします。(2025年3月17日)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ