前回はトランジスタで構成されるデジタル回路について説明した。今回も引き続き、プロセスの基本的なことを解説していく。テーマはロジック回路、それと同期/非同期回路についてだ。

ロジック回路実験基板

プロセッサー内部の基本となる

ブール代数とロジック回路

デジタル回路、あるいはロジック回路と呼ぶこともあるが、これの基礎になっているのがブール代数という記号論理学である。最初にこれを発案したのは19世紀の数学者であるGeorge Booleで、彼の名をとってブール代数(Boolean Algebra)と呼ぶ。

もっともブール代数そのものがロジック回路に出現するわけではなく、このブール代数をベースに考案された、組み合わせ回路と呼ばれるものが広く使われている。

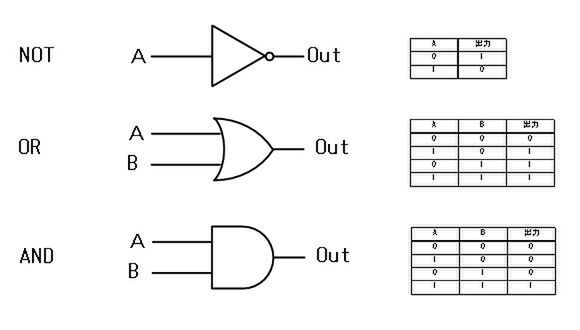

その一番基本的なものが、図1に示す3つである。NOTは唯一の1入力で、入ってきた信号をひっくり返すもの。入力Aが0なら1を、Aが1なら0をそれぞれ出力する。前回インバーターとして示した2つのMOSFETを組み合わせた回路が、このNOPとして動く。

他に、AとBの2つの入力の「どちらかが」1だったら1を返すOR(論理和)、それとAとBの「両方が」1だった時のみ1を返すANDがある。これを組み合わせることで、さらにNOR/NAND/XORといった回路(図2)も考えられる。

NORはOR+NOTで「AとBが両方0の時だけ1」だし、NANDはAND+NOTで「AとBが両方1の時だけ0」である。XORはORの拡張版で、「AとBの値が異なる時だけ1」といった働きをする。このNOR/NAND/XORあたりまでを「基本的なロジック回路」と分類することが多い。

もっと厳密に言えば、NANDとNOR、NOTがあれば、残りの3種類のロジック回路をすべて作れるので、基本的という場合にはNANDとNOR、NOTの3つを指すこともある。

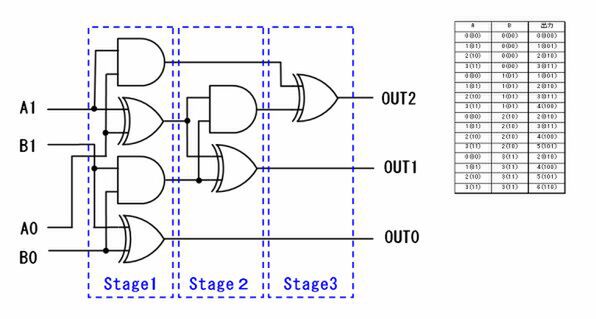

さて、これを組み合わせるとなにができるかだが、実はプロセッサーの内部回路は全部この組み合わせだけでできている。つまり6種類だけで全部片付くわけだ。一例として、図3には2bitの加算器(Adder)の例を示した。

2bitの入力AとBは、どちらも0~3の値を取る。なので、組み合わせとしては0~6の範囲の結果が出ることになる。別にこの回路そのものを理解する必要はないのだが、簡単に説明すると以下のとおりになる。

| Stage 1 | A0とB0、A1とB1をそれぞれ加算する(XOR)とともに、桁上がりの計算も行なう(AND) |

|---|---|

| Stage 2 | 1桁目(A0とB0)の桁上がり分と、2桁目(A1とB2)の結果を加算するとともに、その桁上がりも計算する |

| Stage 3 | 2桁目の桁上がりを確定する |

この回路は説明用にわざと愚直な実装にしてあるので、実際はもう少しスマートな方法があるし、なによりこの方式では桁が増えるとどんどんStage数が増えてってしまってあまり実用的ではないのだが、それは説明用ということでご容赦いただきたい。

この連載の記事

-

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 - この連載の一覧へ