記憶密度を上げなくても容量を増やす技術「3DS」

問題はやはりコスト面

容量の倍増が困難という問題を抱える一方で、メモリーの大容量化へのニーズそのものは止まらない。これまでであれば、「ではDIMMの枚数を増やすことで対応しましょう」と、チップの数を増やすことでの解決が可能であった。

例えばサーバー向けであれば、2つのDRAMチップを積層して、Wire bondingでつなげるという解決策が多く存在する。ところが厄介なことに、メモリーインターフェースがDDR4世代に切り替わっていくことで「メモリー1chあたりDIMMは1枚」「Wire Bondingによる積層は不可」という制約がつくことになってしまった。

どちらも根っこは同じで、信号が高速化したため、複数枚のDIMMを1つのメモリーチャンネルに接続したり、あるいは1本の信号線から2つのチップに分岐させて信号を引っ張ったりすると、そこで波形が乱れて正常に通信ができなくなるためだ。

逆に言えば、DDR4世代の信号はその位シビアということでもある。実際、DDR4世代で唯一複数枚のDIMMが利用可能なのは、LRDIMM(Load Reduced DIMM)という、信号を一旦バッファで受けるタイプのものだけである。

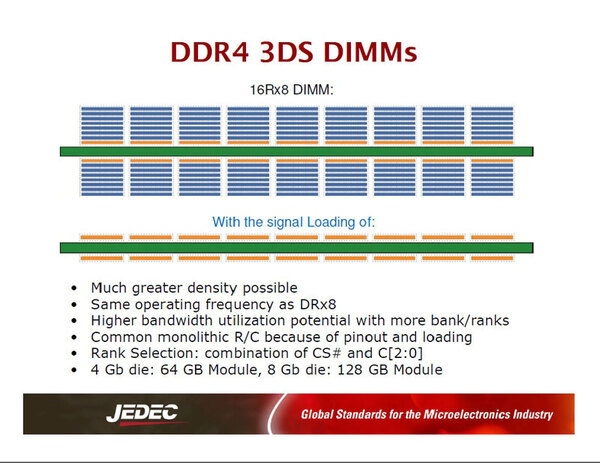

そこでJEDECがDDR4世代のDIMMの解決案として出してきたのが、3DS(3D Stacking)である。最大で8枚のDIMMをTSV(垂直貫通電極)経由で接続することで、DRAMの記憶密度が上がらなくても容量を増やせるようにしよう、という発想である。

今年4月、SK Hynixはこれにもとづいた128GB DIMMの開発に成功したことを発表している(関連リンク)。ベースとなるのは8GbitのDDR4 DRAMで、これを2つ積層したもの、つまりチップあたり16Gbitを、片面あたり32個(DIMMあたり64個)実装することで、128GBの容量を確保したものだ。

しかし、この方式が普及すると見ているベンダーはほとんどない。理由はコストの高さである。定量的な数字を持ち合わせていないのだが、2012年頃の試算では、TSVを使って積層する場合、一般に100mm2あたり2ドルほどのコストがかかるとされている。

内訳は、TSVを作りこむのに大体1ドル、次いで2つのチップをTSV経由で張り合わせるのに大体1ドルである。

DRAMは50~80mm2のダイサイズに納まっているのが普通なので、するとTSVの積層コストは1~1.6ドルという計算になる。恐ろしいことに、このコストにはDRAMそのものは含まれていない。

DDR4世代はまだ高価格なので、DDR3世代で考えると、現状2Gbit品が大体1個あたり0.5ドル程度、4Gbit品は1ドルに満たない程度である。将来はDDR4もこの程度に落ちてくると思うのだが、ここで積層を掛かけた場合

×1:0.5ドル

×2:2.0ドル(DRAM×2+TSV×1)

×4:5.0ドル(DRAM×4+TSV×3)

×8:11.0ドル(DRAM×8+TSV×7)

といった具合に、猛烈な勢いでコストが上がることになる。これはあくまでチップ単位の話だから、これをDIMMに仕立て上げたら、いくらの値札がつくか考えただけで恐ろしい。

行き詰まった感が強いDRAMのプロセスは

用途別に構成を変え最適化することで対処

今回はだいぶ市場経済の話になってしまったが、いろいろと行き詰まり感が強いのが現状のDRAM向けプロセスという話である。

少なくともDDR4世代ではこれまでのように、微細化で低価格化と大容量化・高速化が実現できるという話はもうまったくなく、あとは高速メモリーなのか、大容量メモリーなのか、省電力メモリーなのかという具合に、用途別にメモリーの構成が変わりつつある。

それに応じてプロセスの最適化の方向が違う傾向になりつつある。短期的には、各社ともDDR4よりは早期に立ち上がり、しかもニーズが多いLPDDR4に重点的なシフトを敷きつつあり、この結果DDR4の立ち上がりがやや後送りになっている。

幸いにもというか不幸にもというか、DDR4の最初のプラットフォームである“Haswell-E”はなにしろあまりに限られており、本格的にDDR4を利用する“Sky Lake”は来2015年後半まで出てこないと思われるので、多少DDR4が遅れても問題はないのだろう。

ただこうした動きはプロセスの微細化をさらに遅らせる方向に作用するわけで、むしろ当面はTSVを使った3D積層のコストをどう下げるかの方がコストダウンに効果的だ。それもあり、今後DRAMの微細化はかなりスローになってゆくであろう、というのが筆者の観測である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ