分子の間隔を広げ、電流を速く流す

歪シリコン

これと同じ時期に、トランジスタの高速化に関してもう1つ新技術が登場した。2001年にIBMが京都で開催した「2001 Symposium on VLSI Technology」で発表した「歪シリコン(Strained silicon)」である。

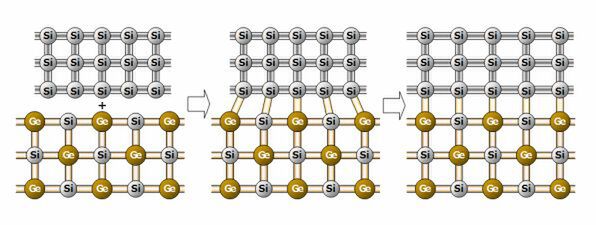

これはどんなものかというと、まずSiGe(シリコンゲルマニウム)の膜を形成し、その上にシリコンの膜を形成する。両者は格子定数(それぞれの分子の間隔)が異なっており、SiGeの方が大きいのだが、格子定数の大きなSiGeの上にシリコンを形成すると、シリコンの方が引っ張られて、本来よりも大きな格子定数になった(=歪んだ)シリコンができあがるというものだ。

ちなみにSiGeを使うのはPMOSの場合で、NMOSの場合はSiN(窒化シリコン)を使うことで同様に歪ませることになる。

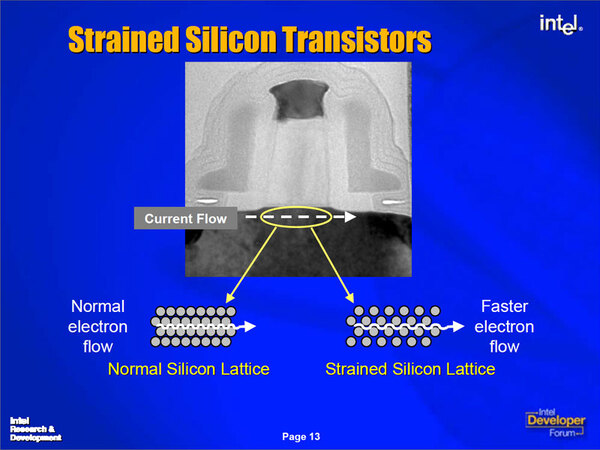

こうしてシリコンを歪ませると利点が生じる。電流が流れるという現象は、自由電子が格子間を移動していくのであり、格子が大きくなるほど速く電流が流れることになる。これはそのままスイッチング速度の改善につながるわけだ。

この歪シリコンの効果であるが、「2004 Symposium on VLSI Technology」においてインテルが発表した情報は以下の通りだ。

- PMOSは、駆動電流が30%向上。逆に同一駆動電流であれば、歪シリコンを使わない場合と比較してサブスレッショルド・リーク電流が50分の1に削減

- NMOSは、歪シリコンを利用することで駆動電流が10%向上

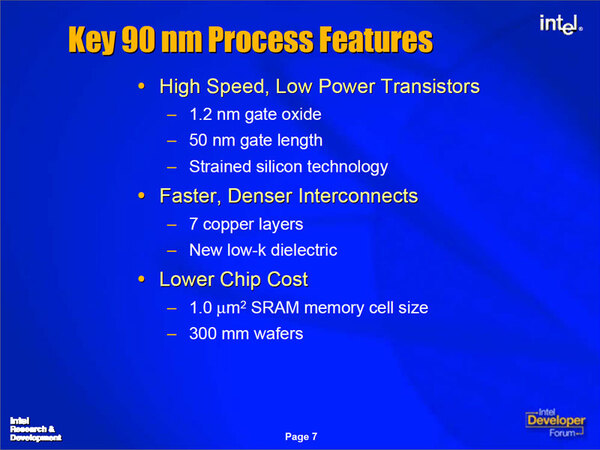

時期が前後したが、インテルは2003年に、この歪シリコンを利用した「P1262」プロセスを発表する。

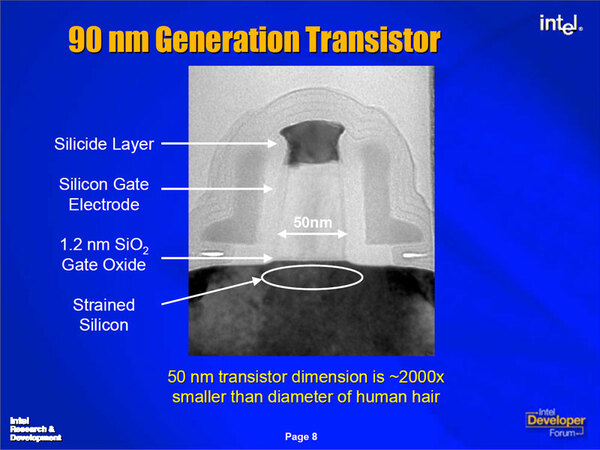

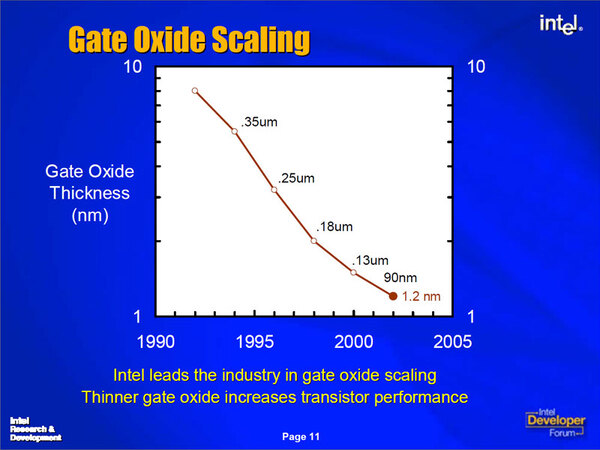

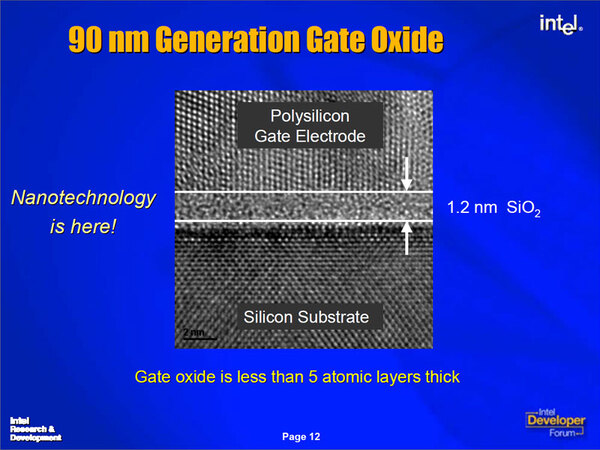

歪シリコンを利用した最大のものがトランジスタであり、ゲート長はわずか50nmしかない。さらには、ゲート酸化膜の厚みも急速に減じており、P1262ではわずか1.2nmまで縮小された。1.2nmというと「原子5つ分よりも薄い」というレベルである。

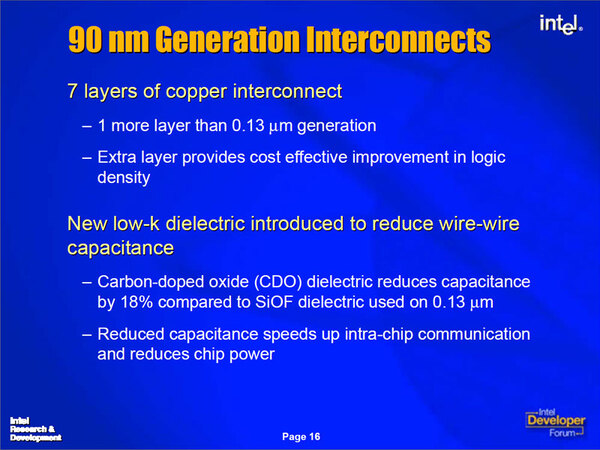

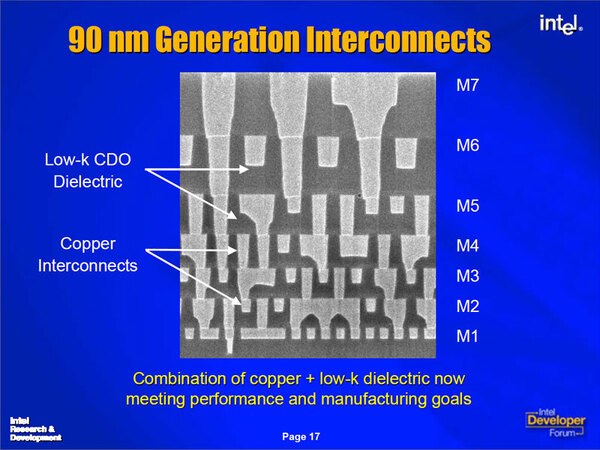

他の特徴としては、P1262では7層の配線層が利用できるようになったが、この配線層の絶縁体には、ただのシリコンに代わって低誘電率(Low-K)絶縁体を利用するように改善された。

複数の配線が近接している場合、配線間容量と呼ばれる仮想的なコンデンサーにあたるものが生成されてしまう。この配線間容量に比例して信号遅延が起きるため、なるべく容量を小さく抑えないといけない。

誘電率は配線間容量に関係するもので、他の条件が同じなら誘電率が大きいほど配線間容量も大きくなる。そこで誘電率の低い絶縁材料を配線層に利用することで、配線間容量を低く抑え、信号速度の低下を抑えたのだ。

余談になるが、インテルは歪シリコンの技術に関して、2005年7月に米AmberWave Systems(現AmberWave)から特許侵害の訴えを起こされており、2007年3月に和解している(関連リンク)。和解条件は不明だが、インテルはAmberWave Systemsから10年間のライセンスを受けることになったため、なにかしらの侵害があったのだろう。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ