リーク電流の増加が

消費電力の増加を招く

ここまではインテルの発表による、すばらしいポイントを説明してきたわけだが、結果がどうだったかはご存知の通り。恐ろしいほどのリーク電流により「Prescott」や「Tejas」を死に追いやった元凶とされている。

なにが悪かったかといえば、ゲート・リーク電流が無視できないほど大きかったという一点に尽きる。なにしろゲート酸化膜の厚みが1.2nmまで薄くなると、もう量子トンネル効果で絶縁体を超えて電流が流れてしまえる域に達しており、このままでは打つ手がない状態だった。

ちなみに他社のプロセスどうであろうか。具体的に公開しないファウンダリーのほうが多いのだが、STMicroelectronicsは、130nmプロセスが2nm厚、90nmプロセスが1.6nm厚であることを学会論文で公表している。

また、複数のファウンダリーをサポートしたシミュレーションツールのパラメーターでは、130nmプロセスで3~2.5nm厚、90nmプロセスで2~1.5nm厚程度に設定されており、相場としてはこのあたりなのだろう。

実際インテルでも130nmプロセスの1.5nm厚ではここまでGate Leakageは多くなかったわけで、それを1.2nmにまで削った結果として「一線を越えてしまった」と考えればいい。

実はインテルもこの事を理解していた。頭では理解していたつもりなのに、体が理解していなかった。だが、Pentium 4の惨状で体でも理解したというべきだろうか。

2003年11月にインテルはHKMG(この話は次回)に関する発表を行なったが、この発表の中でP1262のGate Leakageがシャレになっていないことを間接的に認めている。

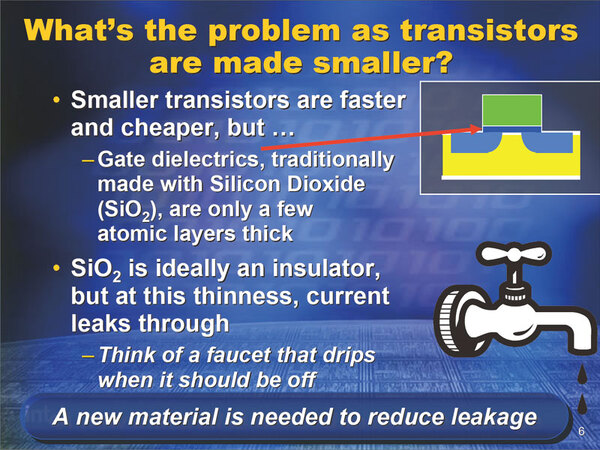

ゲート絶縁体には通常シリコン酸化膜が理想的な材料だとしつつも、薄すぎてもはやリークを止められないため、新しい「材料」が必要であると明確に示している。

ただこの「材料」を既存のCMOSプロセスに組み込むのは至難の業であり、解決しなければいけない問題が多数あるため、「今すぐ使います」というわけにはいかなかった。

インテルが新しい材料を導入したのは、2007年に投入した45nmプロセスの「P1266」からだ。他のベンダーはもっと遅く、GLOBALFOUNDRIESは32nm SOIプロセス、TSMCは28nmプロセスからになっている。その意味では相変わらずインテルは先頭を突っ走っていたわけだが、そのインテルにしても65nmプロセスの「P1264」はどうにもならなかった。

結局インテルはP1264世代では、目立った新技術を導入していない。配線幅65nm、ゲート長30nmであるが、ゲート酸化膜の厚みは1.2nmを維持している。では変更点はなにかというと、まずPMOSに関してはゲルマニウム濃度を高めて歪みの大きさを80%増大、同様にNMOSに関しても「Si3N4」という材料を利用することで、やはり歪みの大きさを80%増大させている。

これによって、酸化膜の厚みを減じなくても性能を大幅に改善することに成功している。このトランジスタの性能改善を、速度向上ではなくリーク削減に振ったのが大きな特徴である。

結果として65nm世代のPentium 4やPentium Dは大幅に消費電力を削減することに成功した反面、動作周波数は90nm世代と同等に留まったのは致し方ないところであろう。

もっともインテルにとって幸いだったのは、Pentium Mの系列で積極的にClock Gatingを導入したり、そもそもターゲットとなる動作周波数を落としたことで、より省電力なトランジスタを利用する対策が講じられたことである。

これにより、問題の多かったP1262を使った「Dothan」は、十分AMDと競合できる性能/消費電力比を実現でき、65nmの「Core 2」はIPC(Instructions Per Clock)を高めることで、動作周波数を抑えて性能を引き上げられたため、P1264に課せられた「トランジスタは高速だが、それを動作周波数の向上に振ってはいけない」という制約はあまり問題にならなかった。

以上のことから、65nm世代はインテルにとって初の「微細化しながらも動作周波数を引き上げられない」プロセスとなった。実際プロセスノードとトランジスタの微細化だけは実現したものの、それ以外の新技術はなにも導入しておらず、ある意味「停滞」と評されても文句が言えない世代である。

それもあってか、P1264に関してはプレゼンテーションなどもそう多くない。その分次のP1266ではいろいろ爆発することになるが、それは次回説明しよう。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ