インテルは8月8日、同社の14nmプロセスの詳細と、これを採用したBroadwell-YことCore Mプロセッサーの詳細を突如として公開した。Core Mに関しては次回説明するとして、今回は14nmの詳細について解説したい。

情報を出そうにも出せない14nmプロセス

製造の信憑性が疑われ始める

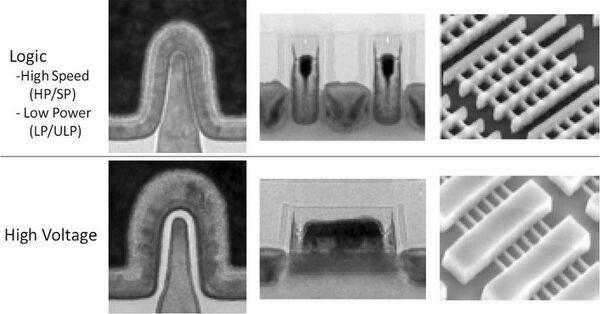

連載260回でも述べたとおり、インテルは22nm世代以降でトランジスターの断面写真を出し渋っており、全然公開しないわけではないにしろ、あまり目に触れる形では出してこなかった。特に14nmプロセスに関してはIEDM 2013でも公開されておらず、これは「まだ量産レベルの14nm FinFETが製造できていない」と受け取られても仕方がない状況だった。

余談になるが、ここで例えば実験室レベルのFinFETの写真を「量産製品です」といって出したとする。もちろんその時には競合メーカーは「うぉーすげー」と驚くわけだが、後で量産品が出回ったら当然のようにその断面構造などをSEM(走査型電子顕微鏡)やTEM(透過型電子顕微鏡)を使って確認のために解析することになる。

実際世間には、こうしたチップの分解・解析のサービスを専門に行なっている業者もあるほどで、設備さえあればそう難しい作業ではない。この解析結果が学会に発表されたものとまったく違ったりすると、当然「ちょっと待て」という話になる。

こうしたことが抑止力になって、学会で大嘘をつくのは難しい。特にインテルのようなテクノロジーリーダーの場合、競合メーカーがその技術に追いつこうとすべく待ち構えているため、なおさらである。

話を戻すと、そんなわけでインテルとしては情報を出そうにも出せない状況が続いていたのが14nm FinFETということになる。ただその間にもAlteraに続き、PanasonicのSoCの製造を受託することが発表(関連リンク)されるなど、14nmの生産能力に見合った需要は創出できたので、後は生産するだけという状況になった。

こうなってくると、そもそも14nmプロセスがちゃんと製造できていることを内外に示す必要がある。AlteraやPanasonicといったメーカーには個別にもっと詳細を示しているとは思うが、それを広く対外的に示すのと示さないのでは信憑性に差が出てくる。

スケジュールを考えれば、もう1ヵ月待てばIDFというお披露目の場があるのに、それに先行してアピールしたのは、いい加減に詳細を公開しないと14nmプロセスの信憑性そのものが疑われかねない状況になりつつあることと、やっと14nmプロセスが安定して、詳細を出しても問題ないレベルになったことの両方と考えて良いだろう。

ようやく公開された

14nmプロセスの構造

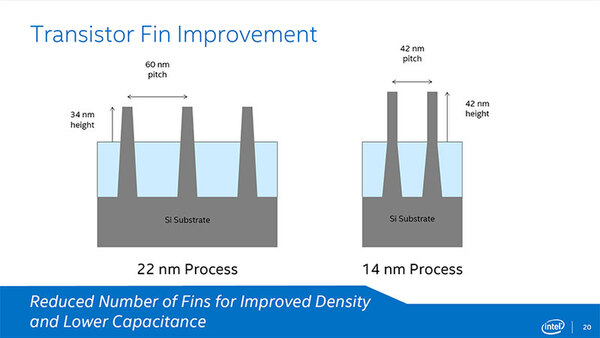

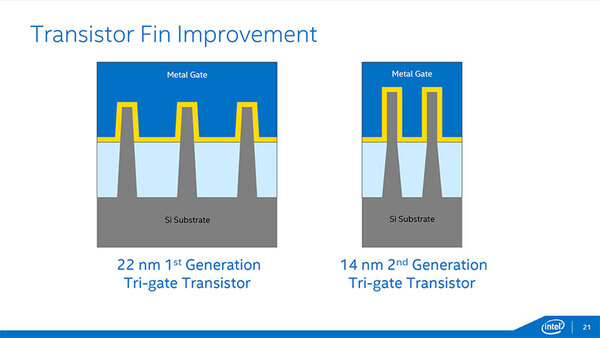

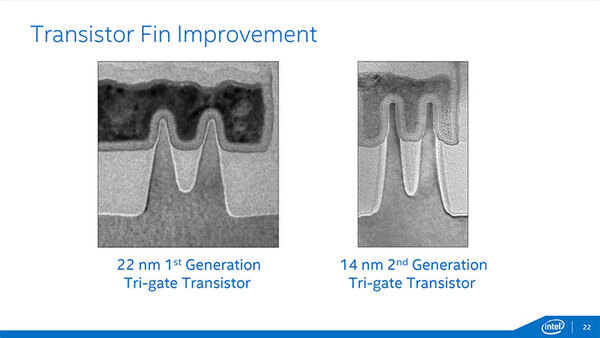

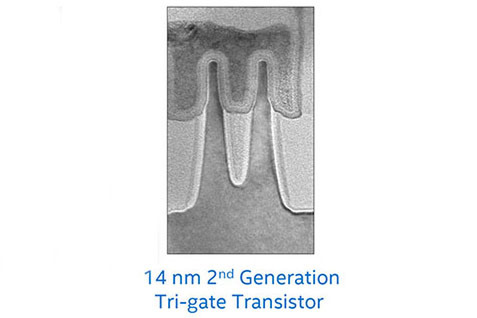

さて左下の画像が14nm FinFETの概要である。まずトランジスタの構造そのものであるが、従来に比べてフィンのサイズを高く、かつ狭くしていることがわかる。

またフィンの間隔そのものも縮められており、同じ面積により多数のフィンを構築できるようになったとする。もちろん実際にはこのフィンの上に絶縁層を挟んでメタルゲートが構築されている形だ。

実際のトランジスタをTEM(透過型電子顕微鏡)で見たのが下の画像で、ずいぶんフィンの形状が異なるのがわかる。

22nm世代は、言ってみれば三角形の山を作り、その上の部分のみをフィンとして使う形なのに対し、14nmでは明確に三角形の頂点部分の幅を削ったような形になっているからだ。

こうして削るのは、High-K絶縁膜の形成時に問題があるためだろう。もし幅を削らないままだと、2つのフィンの間が狭すぎて、絶縁膜の形成に問題が出てきそうだ。フィンの間隔を42nmまで縮めるためには、フィンそのものの厚みも減らさないとうまくいかない、ということだったと想像できる。

→次のページヘ続く (配線層も微細化し、実装密度を向上)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ