微細化が困難で、高密度化もそろそろ限界

ロードマップから紐解くDRAMの展望

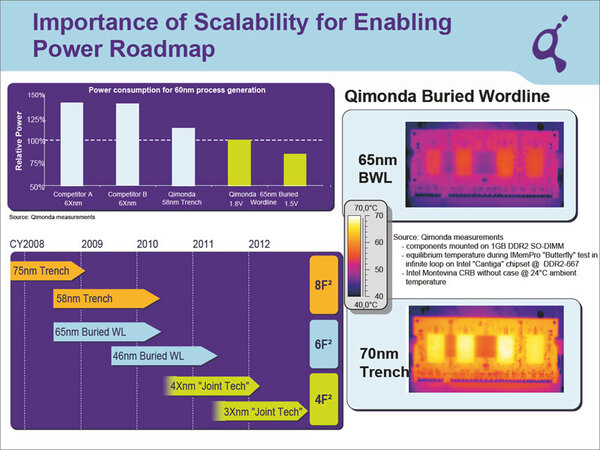

下の画像は2008年のIDFにおいて、今は存在しないQimonda(※)の示したロードマップである。

※旧Infineoのメモリー部門が分社化したメモリーメーカー。一時期は世界No.3のポジションだったが2009年に破綻した。

Qimondaの場合、トレンチ型からスタック型への切り替えが予想より時間がかかり、これが破綻の1つの要因になったのだが、それはともかくとして2009年頃から6F2に切り替え、2011年からは8F2に移行する予定だった。

加えてプロセスの微細化も進めており、これによって大容量化を進める方向性を示していた。時期や実現するプロセスなどは、メモリベンダー各社によって若干違いがあるものの、基本的にはこの方向性でいけると考えていたのが2008~2009年という時期である。

ではその後、これがどう変遷していったのかを、ITRSのロードマップから引用したい。表1は、2008年~2013年のITRSのロードマップのPIDS(Process Integration, Devices, and Structures)の中で、DRAM Requirementの中にあるプロセスノードをまとめたものである。

縦軸が何年のロードマップかを示し、横軸はそのプロセスノードが何年に実現できるとみなしているかを示している。

| 表1 DRAM Pitch | ||||||

|---|---|---|---|---|---|---|

| 2008 | 2009 | 2010 | 2011 | 2012 | 2013 | |

| 2008 | 58 | |||||

| 2009 | 50 | 52 | ||||

| 2010 | 45 | 45 | 42 | |||

| 2011 | 40 | 40 | 36 | 31 | ||

| 2012 | 36 | 36 | 31 | 28 | 28 | |

| 2013 | 32 | 32 | 28 | 25 | 25 | 28 |

| 2014 | 30 | 28 | 25 | 22 | 22 | 26 |

| 2015 | 25 | 25 | 24 | 20 | 20 | 24 |

| 2016 | 22 | 23 | 21 | 18 | 18 | 22 |

| 2017 | 20 | 20 | 18 | 16 | 16 | 20 |

| 2018 | 18 | 18 | 16 | 14 | 14 | 18 |

| 2019 | 16 | 16 | 14 | 13 | 13 | 17 |

| 2020 | 14 | 14 | 13 | 12 | 12 | 15 |

| 2021 | 13 | 13 | 12 | 11 | 11 | 14 |

| 2022 | 12 | 11 | 10 | 10 | 10 | 13 |

| 2023 | 10 | 9 | 9 | 9 | 12 | |

| 2024 | 9 | 8 | 7 | 7 | 11 | |

| 2025 | 7 | 6 | 6 | 10 | ||

表を見てみると、2008年あたりのロードマップは保守的で、2013年あたりのロードマップに近いことがわかる。

逆に積極的なのが2010~2012年あたりで、2015年には20nmプロセスで製造に入り、2016年以降は20nmを切るとしている。ところが2013年のロードマップを見ると、2017年あたりまでは20nm台が維持され、10nm台に入るのは2018年以降となっており、2年ほど後送りになっている。

もっとおもしろいのは表2で、これはセルのサイズファクター、つまり6F2か4F2かを示すものだが、2008年はずっと6F2が続くとしている。

これに対し、2009年以降はほぼ3年後に4F2になるとしているが、導入時期が毎年1年づつ後送りになっている。要するに、ずーっと「あと3年」の状態から進歩していないわけだ。

| 表2 Cell Size Factor | ||||||

|---|---|---|---|---|---|---|

| 2008 | 2009 | 2010 | 2011 | 2012 | 2013 | |

| 2008 | 6 | |||||

| 2009 | 6 | 6 | ||||

| 2010 | 6 | 6 | 6 | |||

| 2011 | 6 | 4 | 6 | 6 | ||

| 2012 | 6 | 4 | 6 | 6 | 6 | |

| 2013 | 6 | 4 | 4 | 6 | 6 | 6 |

| 2014 | 6 | 4 | 4 | 4 | 6 | 6 |

| 2015 | 6 | 4 | 4 | 4 | 4 | 6 |

| 2016 | 6 | 4 | 4 | 4 | 4 | 4 |

| 2017 | 6 | 4 | 4 | 4 | 4 | 4 |

| 2018 | 6 | 4 | 4 | 4 | 4 | 4 |

| 2019 | 6 | 4 | 4 | 4 | 4 | 4 |

| 2020 | 6 | 4 | 4 | 4 | 4 | 4 |

| 2021 | 6 | 4 | 4 | 4 | 4 | 4 |

| 2022 | 6 | 4 | 4 | 4 | 4 | 4 |

| 2023 | 4 | 4 | 4 | 4 | 4 | |

| 2024 | 4 | 4 | 4 | 4 | 4 | |

| 2025 | 4 | 4 | 4 | 4 | ||

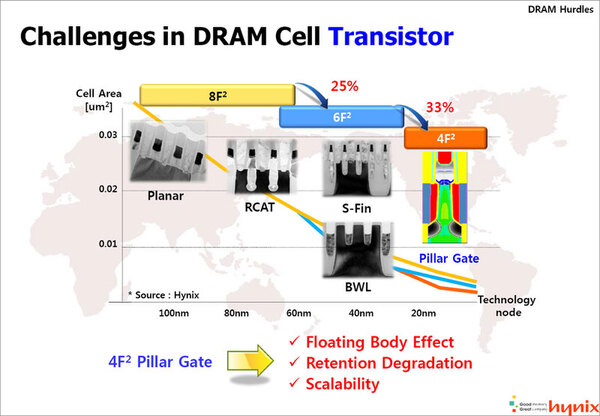

なぜ「あと3年」が続いているかというと、4F2を構成するにはWord LineとBit Lineの間にFETを縦構造で構築する必要があり、おまけにこのFETはプレーナ型を縦にしたというよりはFinFETに近い構造が必要とされる。結果として、このトランジスタを量産するのが非常に難しいという話である。

これもやや古い資料だが、2011年にSK Hynixが示した下の資料では、4F2は20nm以下になるまで導入されないことになっており、表2と組み合わせた場合、実際には2018年あたりまで導入されない見込みである。

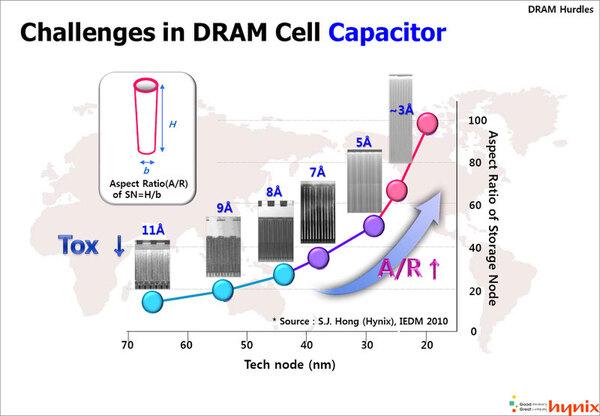

そもそも、プロセスの微細化そのものが表2の通りに行くと考えているベンダーそのものがほとんどいない。ベンダーが20nm台で足踏みしているのは、トランジスタ自身もさることながら、トレンチの方がもう微細化が無理という話が強いからだ。 下の画像はこれを示したものだが、20nm世代になるとコンデンサーの直径は3Å程度になり、縦横比は100倍にも達する計算になるという。これはかなり難易度が高い。

結果としてどうなるかというと、高密度化が止まることになる。プロセスの微細化が無理で、かつセルのサイズファクターも当面変わらないとなると、同一ダイサイズで実現できるDRAMの容量は増えないことになる。

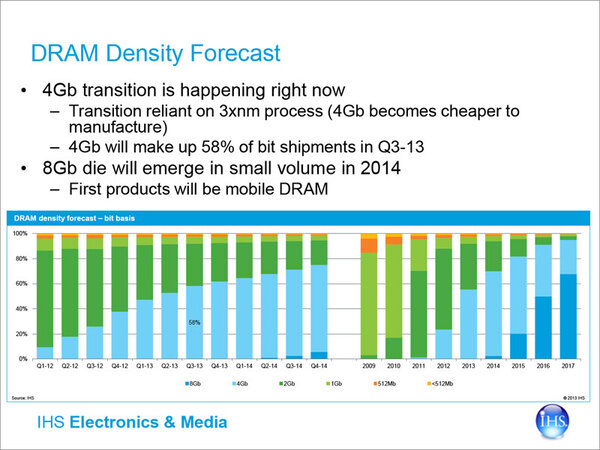

下の画像は、2013年のIDFにおけるインテルが発表した資料だが、このスライドの右側に着目されたい。今は4Gbit品が主流であるが、今年から少しづつ8Gbit品が投入されるとある。これはDRAMチップ1個あたりの容量で、2016年にはこの8Gbit品が主流になるとある。

問題は、この8Gbit品は既存の20nm台のプロセスで製造できるが、次の16Gbit品は20nm以下で、かつ4F2でないと難しく、これが実現する時期が今もって未定なのである。これまでDRAMはほぼ3年程度の周期で容量が倍増してきていたが、ついにその流れが止まりそうなのが現状だ。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ