AMDのロードマップアップデートが終わったので、再び先端プロセスの話に戻ろう。今回は、非常に広くその技術が知られており、かつ効果があることもわかっているにも関わらず、製品への採用例が皆無という「Body Bias」について説明したい。

微細化の天敵であるリーク電流を抑える

Body Bias

Body Biasは、連載246回で少しだけ触れたが、ゲート・リーク電流を抑えるのに有効な方法である。今回はその詳細を解説しよう。下図は、連載236回で説明したMOSFETの構造の概略である。今回のテーマはこのゲートである。

MOSFETの構造。説明の都合上、連載236回で示した図の上下をひっくり返している

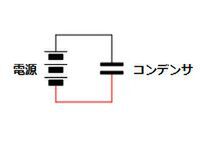

ゲート電圧をかけると、この電圧に応じてドレイン電流が流れるというのがMOSFETの仕組みである。要するに酸化膜がコンデンサーの働きをしてくれるわけで、ゲートから見た等価回路は下図のようになる。

ゲートから見た等価回路

この図で赤く描いた部分が、実は最初の図からは抜けている。いや単に省いただけなのだが、これを描き入れると下図のようになる。つまり、ゲートからかけた電圧は、そのままGNDに落とされているわけだ。これが、ここまで説明してきた一般的な構造である。

ゲートからかけた電圧は、そのままGNDに落とされる

Body Biasはゲート電圧をGNDに落とさずに、下図のように端子を引っ張り出し、ここにも電圧をかける仕組みだ。これにより、トランジスタのスレッショルド電圧が変化したり、トランジスタの特性が変化するという傾向が広く知られている。

Body Biasの仕組み。BIAS端子を引っ張り出し電圧をかける

具体的には、BIAS端子に順電圧、つまりマイナスの電圧をかけるとトランジスタはより高速に、もしくはより消費電力を減らせる一方で、ゲート・リーク電流が増えてしまうことが知られている。逆に逆電圧(プラスの電圧)をかけると、トランジスタそのものの速度が落ちる一方で、ゲート・リーク電流が減るようになる。リーク電流の度合いは、当然ながら電圧によって変化する。

これを利用することで、トランジスタの特性を揃えたり、リーク電流を減らしたりできるというのがBody Biasの骨子である。例えばインテルはMITと共同で、2002年11月に論文(PDF)を発表している。論文は、回路の一部を細かく分割して異なるBIAS電圧を与えることで、特性がどう変化するかをまとめて報告したものだ。

論文によれば以下の結果が得られている。

- 450mVのFBBを掛ける(Forward Body Bias:要するにBIAS電圧に-450mVを掛ける)と、BIAS電圧が0の時に比べて消費電力を23%削減できる

- 450mVのRBBを掛ける(Reverse Body Bias:逆電圧で、BIAS電圧に450mVを掛ける)と、BIAS電圧が0の時に比べてスタンバイ時のリーク電流を7分の2に削減できる

これをもっと積極的に活用しよう、というのが「Adaptive Body Bias」と呼ばれる技法である。これは、トランジスタが動いているときは順電圧を、動いていないときは逆電圧をかけるようにすれば、動作周波数を引き上げつつ、消費電力を減らせて万々歳というわけである。

この連載の記事

-

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 - この連載の一覧へ