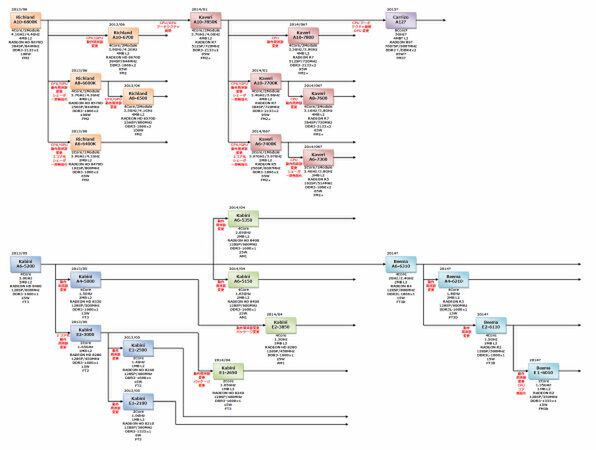

前回に引き続きAMDのロードマップアップデートをお送りしよう。前回のロードマップは2015~2016年に関わる大きな変更を解説したが、今回はもう少し直近の話になる。

Kabiniの後継製品

BeemaとMullins

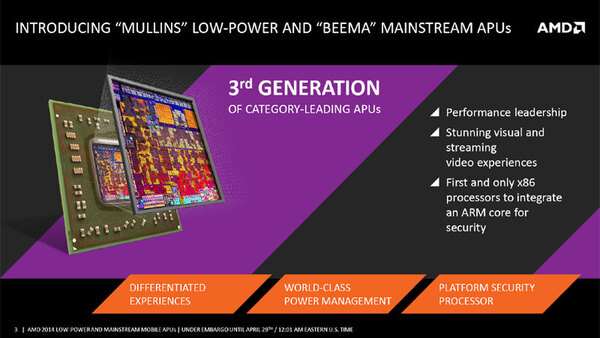

4月29日、AMDはKabini世代の後継製品として、第3世代のAPUである「Beema」と、これの低消費電力型である「Mullins」を発表した。

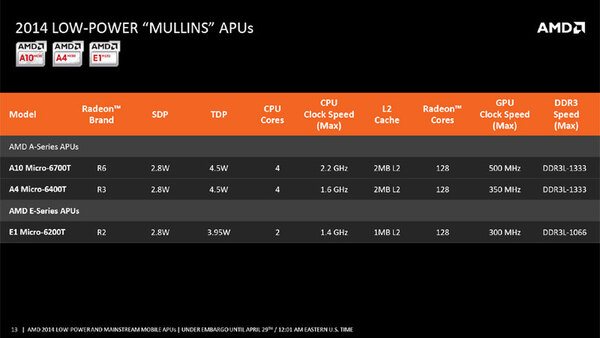

まずは最初に構成を見てみよう。下の画像がメインストリーム向けのBeemaと、低消費電力向けのMullinsの製品ラインナップだ。パッケージはいずれも769ballのBGAのFT3bと呼ばれるもので、現状はマザーボードに直接実装する形での提供となる。2014年後半にはSocket AM1に切り替えて、現在のAthlon/Duronの後継としてリリースする予定があるようだが、具体的なスケジュールやSKUに関しては現在ハッキリしていない。

ちなみに上のロードマップ図ではMullinsは省いてBeemaのみを示しているが、BeemaはともかくMullinsの方はこれまでと異なる“A10 Micro-6700T”といった新しい表記になっている。BeemaとMullinsの特徴をまとめたのが下の画像である。

では、Beemaと前世代のKabiniでどれだけ違いがあるかというと、構成的には以下の程度の違いでしかない。

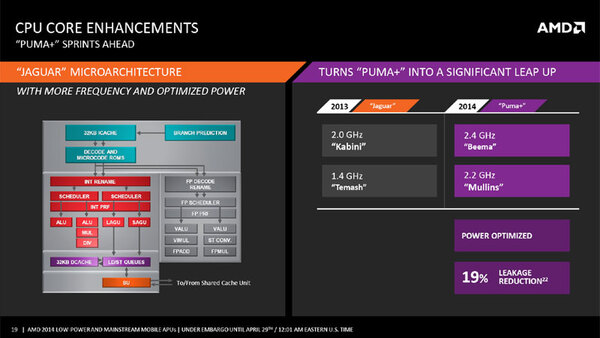

- CPUコアはPumaからPuma+へ

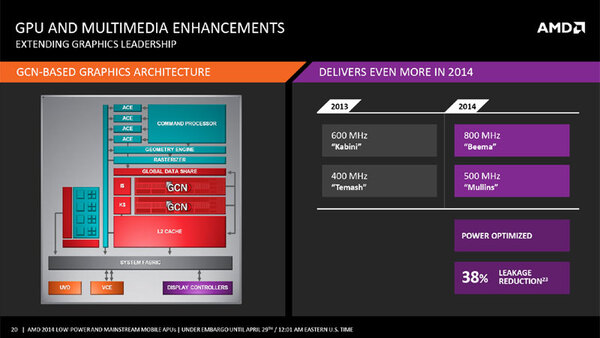

- GPUコアはGCNのまま

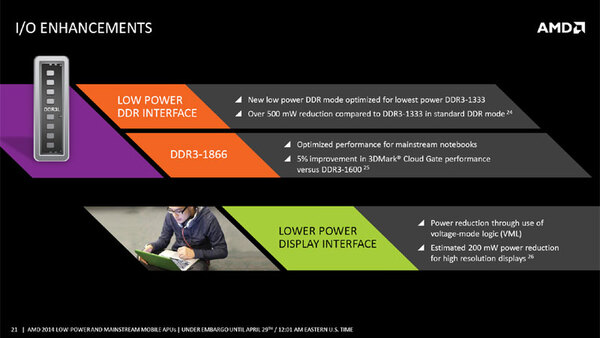

- メモリーはDDR3-1600までの対応からDDR3L-1866までに引き上げ

- 新しく“Platform Security Processor”という名称で、ARMのTrustZoneを搭載

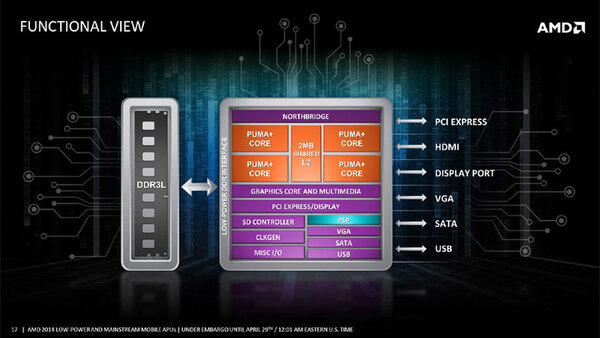

上の画像が全体の構成図であるが、PSP(Platform Security Processor)以外は同じように見える。もう少し細かく見てみると、まずCPUコアが既存のPumaとまったく違いがない。PUMA+の違いは下の画像にもあるように、「より高い動作周波数と省電力化」がメインである。一般論としてこれを実現する場合、パイプラインステージ数を増やすのが得策だ。

パイプラインステージ数を増やすと、1ステージあたりに処理すべき作業が減るため、その分低速なトランジスタを多用しても間に合うことになり、これは省電力化につながる。逆に同等の速度のトランジスタを使えば、1ステージあたりの遅延が減らせるため、その分高速に動作させられることになる。

もちろん、無闇にステージ数を増やすと逆効果というのはPentium 4の例を引くまでもなく、パイプラインの中で致命的になりそうなところをいくつか分割する程度であろう。ただその結果として、CPUコアは同等の消費電力ながらより高い動作周波数が可能になり、消費電力そのものもKabiniが25Wだったのが、Beemaでは15Wに抑えられているわけで、これは大幅な改善になっている。

これはGPUについても同じで、構成そのものは2つのCU(Compute Unit)を搭載しており、トータル128SP(Streaming Processing Unit。AMDの呼び方ならばRadeon Core)で、Kabini世代とまったく同じである。異なるのは動作周波数で、Beemaでは800MHz、Mullinsでも500MHzまで引き上げられている。

もちろんディスクリートGPUと異なり、CPUとメモリーを共有しているうえ、帯域そのものもDDR3L-1866Lなので約15GB/秒といったところで、これをフルに占有してもまだ不足気味ではある。

従って、3DMarkではIce Stormのように描画負荷が軽いケースではあまり性能向上が期待できないが、逆にFire Strikeのように描画負荷が重いケースでは、(絶対性能はともかくとして)相対的に性能改善が大きいと思われる。

その他の項目としては、DDR3L-1866採用のほかに、表示出力の改善などが挙げられている。

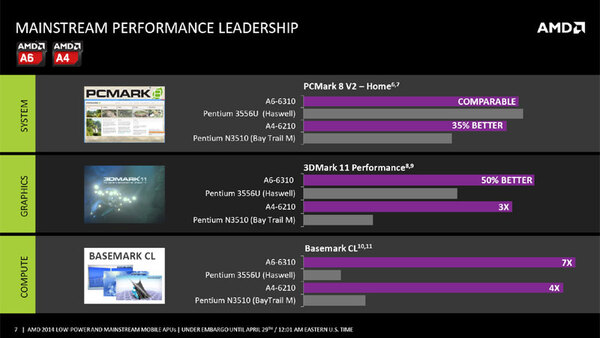

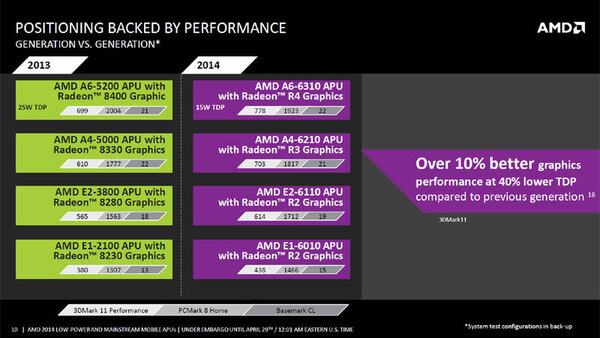

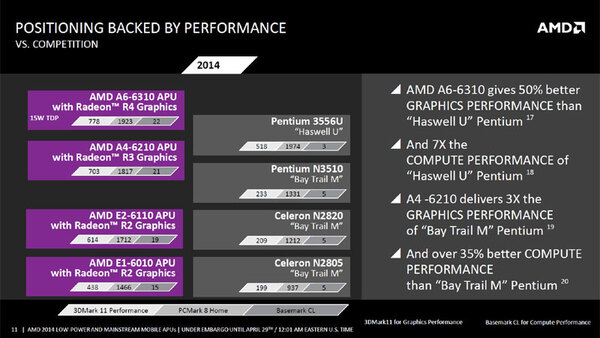

これらの改善でどれだけ性能が向上したのか、下の画像にあるベンチマーク結果で見てみよう。A4-6310 vs Pentium 3556Uという比較では、PCMark 8のHomeでは互角、3DMark 11では50%優位としているし、Bay Trail-MベースのPentium N3510とA4-6210の比較ではPCMark 8が35%、3DMark 11では3倍高いスコアを出せるとしている。

同じAMDの中で比較した場合が下の画像で、特にグラフックの分野では平均して10%の性能アップを、40%の省電力化と同時に実現できたとしている。

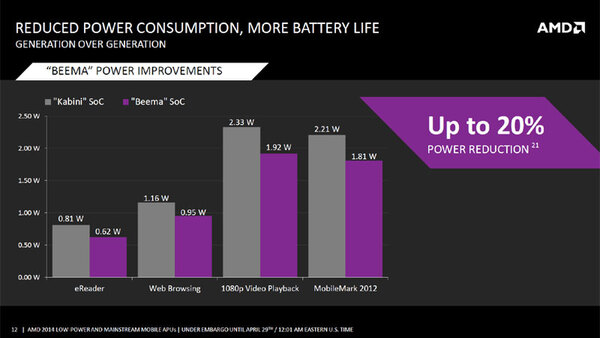

下の画像は、今度はインテルの競合製品と比較したものであるが、より優れた性能だという主張である。最後がバッテリー駆動時の消費電力を比較したものであるが、最大20%の省電力化が可能となっている。

※お詫びと訂正:記事初出時、ロードマップ図におきまして発売日の表記に一部に誤りがありました。訂正してお詫びします。(2014年5月27日)

この連載の記事

-

第781回

PC

Lunar LakeのGPU動作周波数はおよそ1.65GHz インテル CPUロードマップ -

第780回

PC

Lunar Lakeに搭載される正体不明のメモリーサイドキャッシュ インテル CPUロードマップ -

第779回

PC

Lunar LakeではEコアの「Skymont」でもAI処理を実行するようになった インテル CPUロードマップ -

第778回

PC

Lunar LakeではPコアのハイパースレッディングを廃止 インテル CPUロードマップ -

第777回

PC

Lunar Lakeはウェハー1枚からMeteor Lakeの半分しか取れない インテル CPUロードマップ -

第776回

PC

COMPUTEXで判明したZen 5以降のプロセッサー戦略 AMD CPU/GPUロードマップ -

第775回

PC

安定した転送速度を確保できたSCSI 消え去ったI/F史 -

第774回

PC

日本の半導体メーカーが開発協力に名乗りを上げた次世代Esperanto ET-SoC AIプロセッサーの昨今 -

第773回

PC

Sound Blasterが普及に大きく貢献したGame Port 消え去ったI/F史 -

第772回

PC

スーパーコンピューターの系譜 本格稼働で大きく性能を伸ばしたAuroraだが世界一には届かなかった -

第771回

PC

277もの特許を使用して標準化した高速シリアルバスIEEE 1394 消え去ったI/F史 - この連載の一覧へ