微細化するほどパターン転写と エッチングの回数が増えていく

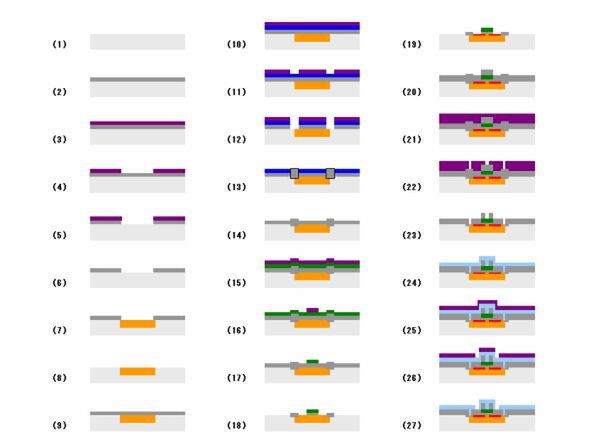

今回延々とこの説明をしたのは、半導体の製造はエッチングと積み重ねの繰り返しということを理解していただくためである。最近ではHigh-K Metal Gateや、歪シリコンといった特殊な材料が利用されているが、これらを構築するためには、延々と積み重ねとエッチングを繰り返す必要がある。実際図5の事例ですら5回もエッチングを行なっているわけで、これが最近では10回を軽く超えているという。

さらには、パターンの転写と簡単に書いたが、これも最近はあまりに回路が微細化しすぎて1発でマスクの転写ができない。このためダブルパターニングやトリプルパターニングというようにマスクを数種類用意して、この組み合わせで正しいパターンを転写する必要がある。図5の例でダブルパターニングを利用すると、パターン転写の回数が10回に増えることになる。

加えて、(14)で簡単にシリコン窒化膜を除去と書いたが、これも1発では不可能で、いくつかの手順を経て除去することになる。こうしたものを全部積み重ねていくと、ものすごい手間になるわけで、一昔前が200段階程度だったのが、最近は300段階に達しているという。

さて、ここまででやっとトランジスタの形成には成功したわけだが、実際にはこの後配線層を積層していく必要がある。こちらも絶縁膜の形成→VIAの形成→配線層の形成を順次進めていくため、また延々とパターン転写→エッチングを繰り返していくことになる。最近は配線層の積層もダブルパターニングが必要になってきており、それは手間とコストがかかろうというものである。

こうした手間はプロセスの微細化や新材料の採用にともない、どんどん面倒になってきている。この手間についてはプロセス微細化の進み方に合わせて都度説明していこう。

そこで次回からインテルのプロッセッサーを例に、もう少し最近の半導体製造プロセスを解説していこう。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ