ロードマップでわかる!当世プロセッサー事情 第590回

Radeon Instinct MI100が採用するCDNAアーキテクチャーの内部構造 AMD GPUロードマップ

2020年11月23日 12時00分更新

11月20日、「Radeon RX 6800」シリーズが無事に発売になった。KTU氏によるレビューをご覧になった方も多いと思うが、おそろしくパワフルな製品に仕上がっており、レイトレーシングを利用しない限りにおいてはGeForce RTX 3000シリーズに十分競合できる。

という話はおいておき、今回解説するのは11月16日に発表されたCDNA第1世代を実装する、Radeon Instinct MI100の話である。が、その前に連載587回に誤りがあったため、まずはこれの訂正をしたい。

Smart Access Memoryを利用するのに必要な

Resizable BAR

こちらでSmart Access Memory (SAM)の正体はCCIXを利用したCoherent Memory Accessではないかと推察したのだが、その後AMD本国の関係者から「そうではなく、PCIeでの接続である」という返事が返ってきた。

その後にSAMを利用するためにはBIOSセットアップでを有効にすべしという注意書きが届いて、やっと正体がわかった格好だ(KTU氏もレビュー記事で触れている)。ついでなので、このResizable BARの話をしよう。

BAR(Base Address Register)というのは、PCI ExpressのConfiguration Space(PCI Expressのデバイスを内部で管理するためのメモリー空間)の中にあり、デバイスのメモリー領域をホスト(つまりCPU側)のメモリー空間にマッピングする際のアドレスを格納している。

もともとはPCI Express(の元になったPCI)が32bitアドレスでの動作を想定していたこともあり、BARの扱えるメモリー領域は最大でも256MBに制限されていた。ところが64bitアドレッシングをサポートしたCPUが登場したことで、BARをもっと広げても良いのではないか? という議論が起こる。

最終的にPCI Express 2.0のECN(Engineering Change Notice)として2008年1月22日に、Resizable BARという仕様が追加された。これはBARのサイズを最大512GBまで拡張できるというもので、オプション扱いとなり、PCI Express 2.1以降では正式に仕様に取り込まれているみ(ただし実装は必須ではなく引き続きオプション)。

マイクロソフトはWDDM v2でこのResizable BARに対応したことを2017年4月に表明している。というわけで、SAMは別にDX12やVulkanだけでなく、DirextX 9/10/11やOpenGLでもその効果が期待できるとAMDの関係者からは返事があった。

余談であるが、筆者もHorizon Zero DawnをSAMありで実施したが、問題なく4Kで完走した。KTU氏との違いは、主にマザーボード(筆者はASUS ROG CROSSHAIR VIII HEROを利用)程度であるが、それが理由とも思えないのだが。

CDNAアーキテクチャーを採用したHPC向けGPU

AMD Instinct MI100を11月16日に発表

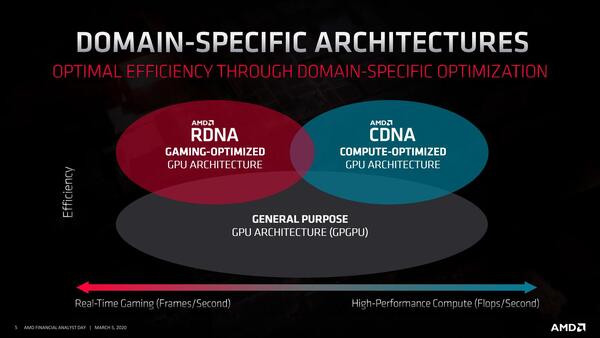

さて、Radeon RX 6800の話はこの程度にして、本題に入ろう。もともとRadeon Instinct系、つまりGamingではなくComputationにフォーカスした市場向けに、AMDは従来のGCN(Vega)からRDNA(Navi)とCDNAに分けると今年3月に明らかにした。

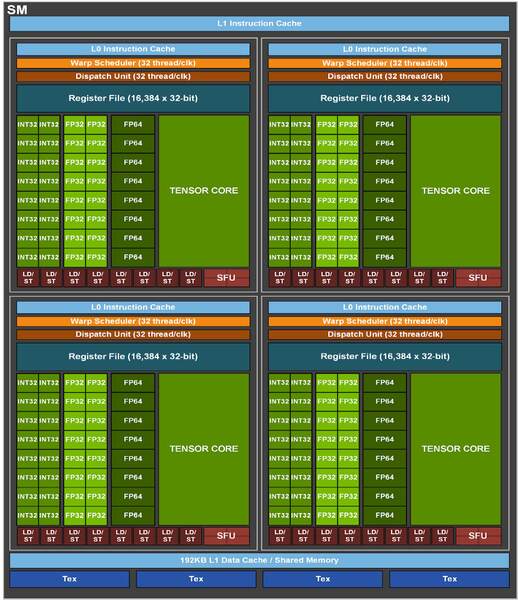

これはNVIDIAも同じで、アーキテクチャーこそ共通のAmpereとされつつ、GPGPU向けのGA100とGaming向けのGA102では、SM(Streaming Processor)の構造が異なっている。GA100はFP64の演算ユニットを搭載する一方でRTコアがなく、逆にGA102はFP64を省いてRTコアを搭載しているのがわかる。AMDはもっと大胆に、アーキテクチャーそのものを切り替えた形だ。

さてその中身である。ちなみにAMDはまだ“VEGA”や“NAVI”にあたる、CDNAのコード名を公開していない。“Arcturus”という名前がRadeon Instinct MI100のコード名と言われているが、アーキテクチャーの名前そのものではない。ということで、以下CDNA 1.0として表記したい。

そのCDNA 1.0の構造が下の画像となる。RDNAの構造と比較すると、(CU数はともかくとして)例えばPixel UnitやRasterize、RB(Render Backend)など描画に必要な要素がキレイに消えていることがわかる。また、当然ながらGeometry Processorも搭載されていない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ