ロードマップでわかる!当世プロセッサー事情 第590回

Radeon Instinct MI100が採用するCDNAアーキテクチャーの内部構造 AMD GPUロードマップ

2020年11月23日 12時00分更新

CDNAはRDNAにかなり近いが

SIMDエンジンをHPC向けにチューンしている

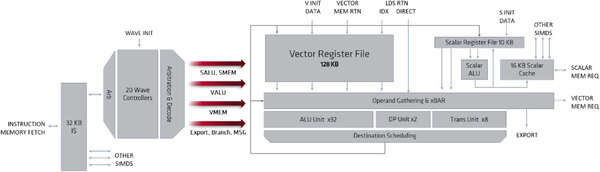

個々のCU(CUDA 1.0ではXCUという名前になっている)の構造が下の画像である。1つのXCUに64個の演算ユニットが実装されるという構図はGCNやRDNAと同じであるが、GCNとの比較で言えば以下の違いがある。

- FP64/FP32のサイクル当たりの処理性能(Vector FP32/FP64)は同じ(FP64で64Flops/サイクル、FP32で128Flops/サイクル)

- 新たに行列演算を高速化するMatrix Unitと呼ばれる仕組みが入り、これを利用することでFP32だと2倍(256Flops/サイクル)の処理性能になる

- FP16は、GCNだとFP32の2倍(256Flops/サイクル)なのに対し、CDNA 1.0ではこの4倍の1024Flopsサイクルで演算可能

- 新たにBFloat16をサポート。演算性能は512Flops/サイクルになる

XCUはこの演算ユニット4つで構成されるので、1CUあたりFP64で256Flops/サイクル、FP32だと512~1024Flops/サイクル、BFloat16で2048Flops/サイクル、FP16なら4096Flops/サイクルになる計算だ。

フロントエンドを含む全体の構成が下の画像だ。RDNAの構成と比較すると、RDNAがWave32での管理となっており、2つの16-Wideをまとめて32-WideのSIMDとして扱う関係か、Wave Controllerは20 Waveになっているのに対し、CDNAではおそらくGCN同様に64-Waveでのハンドリングしていると思われ、Wave Controllerは10 Waveになっているのが目立つ違いである。Vector Registerの数などはRDNAと共通になっている。

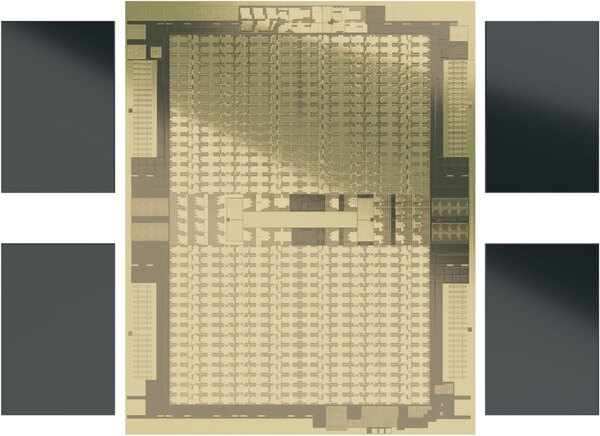

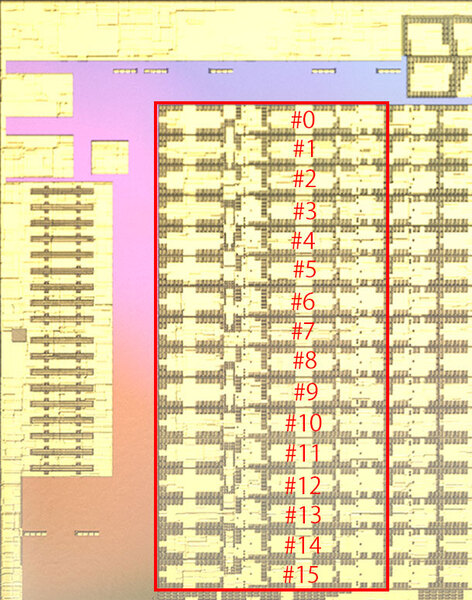

さて、先のCDNA 1.0の構造を示す画像によれば、CDNA 1.0はこのXCUを複数個まとめたグループを8つ搭載することになる。Radeon Instinct MI100の仕様によればXCUは120個なので、グループあたり15個のXCUが含まれる計算になるのだが、実際にダイ写真を見ると、16個のXCUが含まれていることがわかる。

つまりハードウェア的には128XCU、8192個のStream Processorが実装されており、このうち120XCU、7680個のStream Processorのみを有効にしているとわかる。

この理由は後述するダイサイズに関係する。CDNA 1.0は過去最大規模のダイサイズであり、それなりに欠陥を含んでも対応できるように、冗長XCUを8つ用意したというあたりであろう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 - この連載の一覧へ