ロードマップでわかる!当世プロセッサー事情 第590回

Radeon Instinct MI100が採用するCDNAアーキテクチャーの内部構造 AMD GPUロードマップ

2020年11月23日 12時00分更新

ついにAMDもダイサイズが700平方mm超え

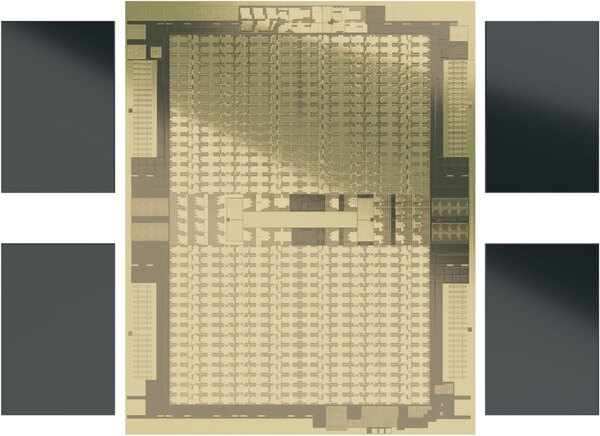

話をダイに戻そう。妙に解像度が低いAMD提供のダイ写真がおそらく縦横比がほぼ正しいイメージと推察されるが、HBM2の寸法から推定するとCDNA 1.0のダイサイズは24.0×31.8mmで763.2mm2となる。ついにAMDも700mm2超えである。NVIDIA A100の826mm2にはやや負けるが、それでもモンスターであることは疑う余地がない。それは冗長XCUを用意しないとまずいのも理解できる。

2 EPYC+8 Radeon Instinct MI100の

理論性能はFP64でおおむね85TFlops程度

さてこのRadeon Instinct MI100であるが、最初のターゲットはオークリッジ国立研究所のFrontierであろう。連載510回で触れたが、オークリッジ国立研究所はAMDのカスタム版EPYC+Radeon Instinctの構成で1.5 EFlopsの性能のFrontierを2021年からインストール開始し、2022年に運用開始となる。

ただ、連載510回の後半で書いたように、本命となるのは5nm世代のEPYC+おそらくCDNA 2.0ベースのRadeon Instinctである。

これに先駆けてオークリッジ国立研究所ではソフトウェアの移植を進める必要がある。すでにオークリッジ国立研究所はAMDの開発キット「ROCm 4.0」をベースにソフトウェアを開発すると表明しており、このソフトの移植のプラットフォームとなるマシンが必要であり、ここに第3世代EPYCと組み合わせたシステムを納入すると思われる。

やや古い話だが、IBMがオークリッジ国立研究所とローレンス・リバモア国立研究所にSierra/Summitを納入する前段階として、POWER8+Keplerベースのシステムが納入されたという話を連載373回で紹介したが、これと同じ話である。

AMDはすでに第3世代のEPYCであるMilanを、特定顧客向けにサンプル出荷を開始していることを明らかにしており、Frontier開発用マシンとしてRadeon Instinct MI100と一緒にオークリッジ国立研究所に納入がスタートしていると思われる。

まだMilanの性能などは明らかになっていないが、例えばEPYC 7742の場合の理論最大性能は2304GFlopsとされており、仮にFPUに関してもALUと同程度に性能が上がったとすれば2700GFlops程度。ということは2 EPYC+8 Radeon Instinct MI100の理論性能はFP64でおおむね85TFlops程度になる。

1ノードで85TFlopsだとすると、これで1.5 EFlopsを実現するためには17647ノードが必要になる計算だ。これは実現不可能な数ではないが、フル稼働時にEPYCが200W、Radeon Instinct MI100が300Wの消費電力だとするとノードあたり2.8KW。これが17600ノードだと消費電力はおよそ50MWになる。

これはCPUとGPUの分だけで、ストレージやインターコネクトの分を含んでないため、これを加味するとざっくり2倍で100MWであろうか? 1Exaflopsあたり66MWというのはやはり大きすぎる。おそらく本番はGenoa(第4世代EPYC)+CDNA 2.0ベースのRadeon Instinctになるだろう。

この世代は5nmに移行することが明らかになっており、確実に消費電力あたりの性能を上げている、つまり同じ性能なら消費電力を下げられるからだ。

その意味では、今回のRadeon Instinct MI100の発表はFrontierやその後に控えているEl Capitanに続くであろうステップを確実に踏んでいることを実証できたという、非常に意味のある発表なのである。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 - この連載の一覧へ