COMPUTEXではチラ見せに終わったNAVIアーキテクチャーとRadeon RX 5700シリーズであるが、6月10日に開催されたNext Horizon Gamingというイベントでその詳細が明らかにされた。概略は先の笠原一輝氏のレポートに詳しいので、こちらでは内部構造に話を絞って詳細を解説しよう。

スレッドの管理を細分化した

RDNAの内部構造

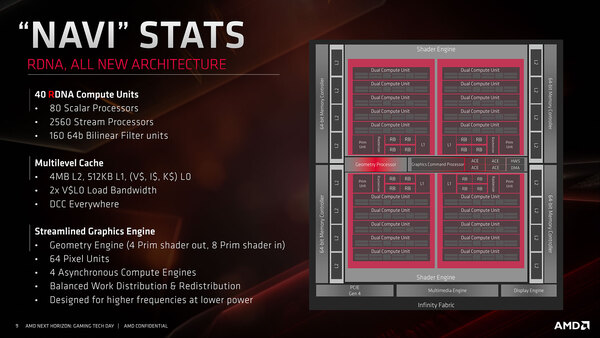

まずRDNAと呼ばれる新しいNAVIの内部構造を説明する。下の画像がNAVI10全体の構成図である。このレベルで言えば、GCNと大きな違いはない。

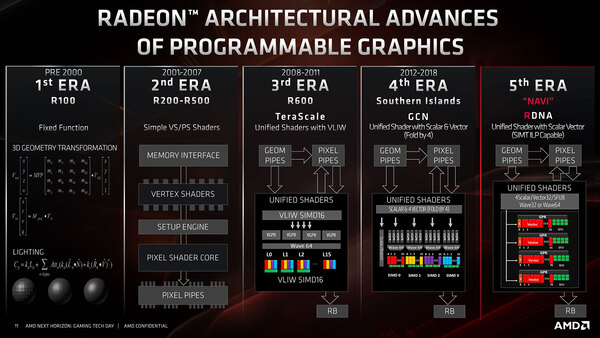

では何が違うか? といえばスレッドの管理の仕方である。R600の世代以降、AMDのGPUは基本的に64スレッドをまとめて管理するWave64という仕組みを取っていた。

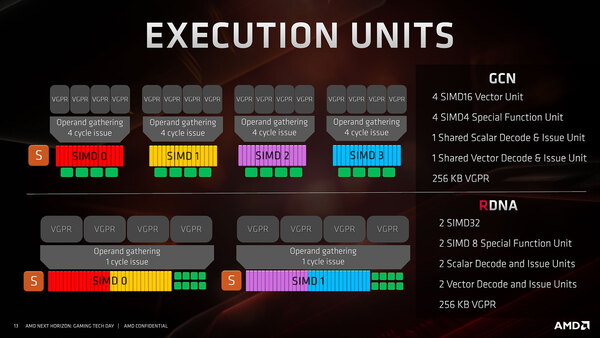

これに対し、RDMAはこの単位を半減化したWave32を基本とする。これにあわせて、Compute Unitの中身も変化した。

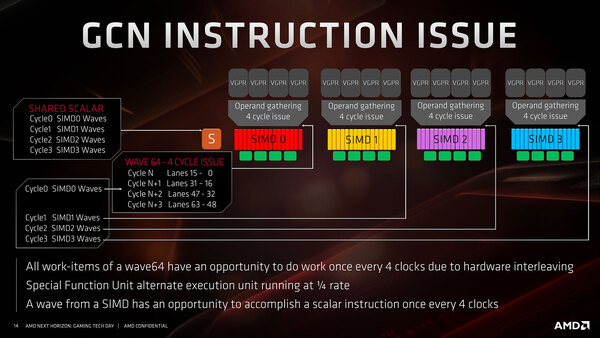

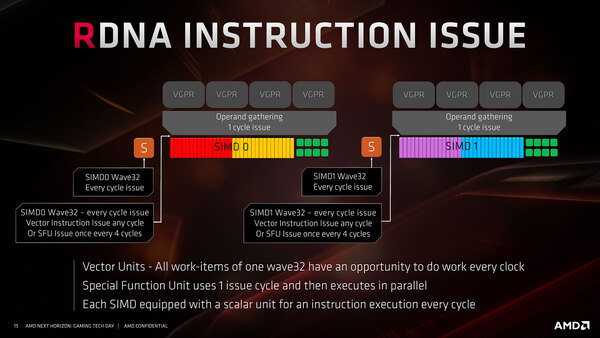

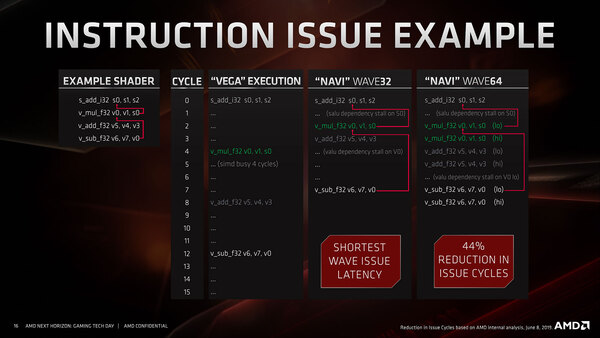

GCN世代では、16-WideのSIMD(Single Instruction Multiple Data)がCU内に4つあり、これが4サイクルかけて4つのWave64を処理する。スループットで言えば1つのWave64あたり1サイクルで処理できるのだが、実際は4サイクル刻みとなっていた。

対してRDNAでは、まずSIMDが32-Wide(内部的には16-Wide×2)構成となり、これが2つのWave32を1サイクルで処理する。

その意味ではスループット的には同じではあるのだが、GCNの場合はそもそも先に書いた通り4サイクルまるまる4つのWave64の処理でロックされる形になっており、また条件分岐などのスカラー処理を行なうスカラーユニットは4サイクルに1回しか動けない(あるWave64がスカラーユニットを使っている間、他のWave64は待機となる)といった弊害があった。

RDNAではこれがすっきりした形になる。ちなみに互換性維持のためにWave64での動作モードも用意されているが、この場合でも構造そのものは変わらず、単にそれぞれの32-WideのSIMDエンジンが2サイクルかけて1つのWave64を処理する、という形になっている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ