前回に引き続き、1月8日に行なわれたCESの基調講演から、今回はGPU周りの話をしよう。AMDが昨年開催した発表会Next Horizonの時点での情報を元にした限りでは、Vega 7nmをゲーミングに持ってくるとは想像できなかったこともあり、連載485回の最後で「ゲーミングGPUに転用するにはやや厳しい」と書いた。

ところが、そうした予想を裏切っていきなりRadeon VIIを発表してしまったわけで、しかも発売日に完売という状況になっている。

すでにRadeon VIIの性能そのものについては加藤勝明氏のレビューがあるのでそちらをご覧いただくとして、そもそもなぜ筆者がRadeon VIIをゲーミングに持ってくると思わなかったのかを説明したい。

7nmに微細化したわりには

ダイサイズが大きすぎる

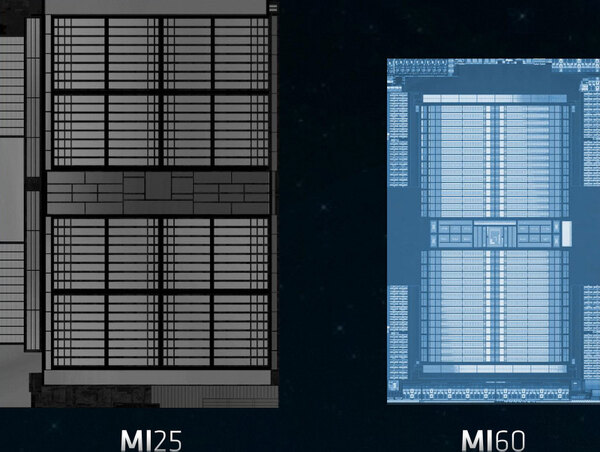

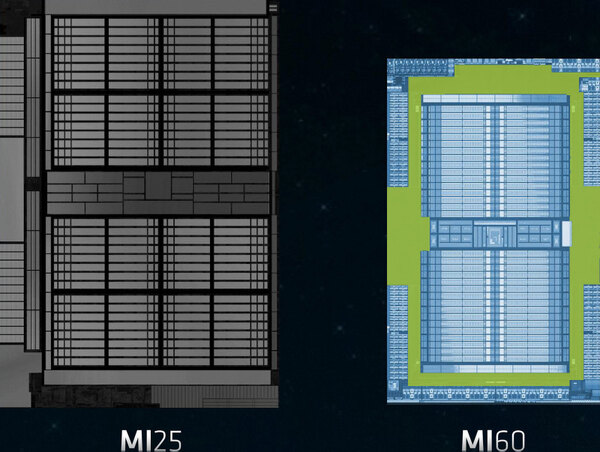

下の写真はNext Horizonにおけるスライドから、Vega 10とVega 20のダイの部分をアップにしたものだ。

Vega 10はダイサイズが486mm2、Vega 20は331mm2と発表されている。「いくらなんでも大きすぎる」というのが、筆者の偽らざる心境である。実際ダイの内部を見ると、Vega 10の方は486mm2をほぼ使い切っているのに対し、Vega 20の方はかなり空きがある。下の画像で黄色くマークした部分は、実際には配線だけが通っている領域と思われる。

面積比で言えば26.8%、89mm2弱が「単に配線だけ」に費やされている計算になる。逆に言えば、パーフェクトな最適化が行なわれていれば、242mm2程度で収まる計算になる。

この最適化は7nm世代ではとても重要である。これが来年以降スタートするEUV(極端紫外線)では多少コストが下がるが、DUV(深紫外線)のマルチパターニングを使うTSMCの7nmの場合、ウェハーコストは16nm世代のほぼ倍近くに跳ね上がると見られているからだ。

おそらくGlobalfoundriesの14nmもTSMCの16nm世代とほぼ同等であり、ということはVega 20は本来Vega 10の半分ほどのダイサイズに抑えないと、原価が一緒にならない。

実際は331mm2と68%ほどにしか縮まっていないので、想定されるチップの原価は36%ほどVega 10よりも高くなる計算だ。つまり、14/16nmで660mm2ほどのダイを製造したのと同等のコストになる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ