Radeon Instinctが年内に出荷開始

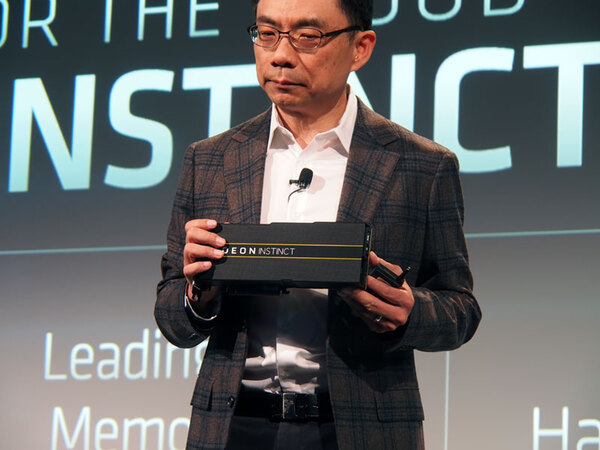

さてそのTSMCのN7を利用する7nm VEGA(VEGA20)、以前連載442回では「出荷は2018年の終わりか、下手をすると2019年になると思われる」としたが、基調講演ではインテルに移籍したRaja Koduri氏の後を引き継いで、RTG(Radeon Technologies Groupエンジニアリング部門を率いるDavid Wang氏がRadeon Instinct MI60を示しながら、これが年内に出荷開始されることを発表した。

まずは今回の発表の内容をまとめると以下の通り。

- 発表されたのはRadeon Instinct MI60とMI50の2製品。主要なスペックは表にまとめたとおりである。ちなみにどちらもTDPは300W。価格は現時点では未公表。

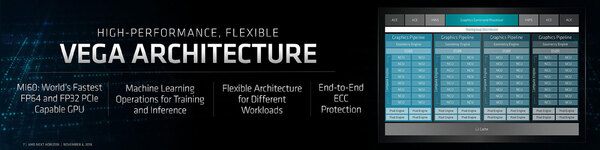

- ダイ(Vega20)はTSMCのN7で製造され、132億トランジスタ。ダイサイズは331mm2となっている。

- 内部構成そのものは既存のVega 10からの大幅な変更はない。

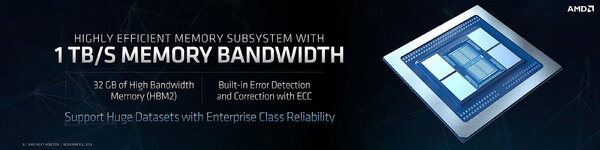

- メモリーはHBM×4の構成に。したがってメモリーバス幅はVega 10から2倍になった計算。

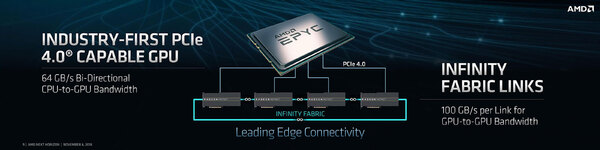

- Vega 20同士の接続は、従来のCrossFire/Native CrossFireに代わってInfinity Fabricによる相互接続がサポートされた。

- SR-IOVを搭載し、複数VMからの同時アクセスや、一つのVMから最大8つまでのGPU利用をサポート。

- AMDが従来からMI向けに提供してきたROCmが2.0になった。

| Radeon Instinctの主要スペック | ||||||

|---|---|---|---|---|---|---|

| MI60 | MI50 | MI25 | ||||

| CU数 | 64 | 60 | 64 | |||

| SP数 | 4096 | 3840 | 4096 | |||

| Max Core Speed(MHz) | 1800 | 1746 | 1500? | |||

| 性能 | Int8(TOPS) | 58.9 | 53.6 | 49? | ||

| FP16(TFlops) | 29.5 | 26.8 | 24.6 | |||

| FP32(TFlops) | 14.7 | 13.4 | 12.29 | |||

| FP64(TFlops) | 7.4 | 6.7 | 0.768 | |||

| メモリー | Capacity(GB) | 32 | 16 | 16 | ||

| Bus | 4096bit+ECC | 2048bit+ECC | ||||

| Clock | 1GHz | 968MHz | ||||

| Bandwidth | 1TB/秒 | 484GB/秒 | ||||

| Infinity Fabric Bandwidth | 200GB/秒 | N/A | ||||

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ