CyrixとCentaur(IDT)を買収してCPUメーカーとなった台湾VIA Technologies社(以下VIA)。前回に引き続き、今回は買収後のVIAのCPU開発について語ろう。

出たり消えたり、紆余曲折したVIA/Centaurのロードマップ

VIAの子会社として引き続きCPU開発を担当するCentaurは、その後も順調に開発を進める。もともとCentaurは人員数十名という、CPU設計会社としては異様なほどに小規模なだけに(後述するNehemiahの頃で70人程度と、当時のCEOであるグレン・ヘンリー氏に聞いた記憶がある。現在も100名程度のはずだ)、インテルやAMDのように毎年や2年ごとに新製品や新アーキテクチャーを投入する、というのは到底不可能である。その結果、平均3年程度で新製品が投入されるというゆったりしたペースになっているが、マーケットを考えればこれで十分というところなのだろう。

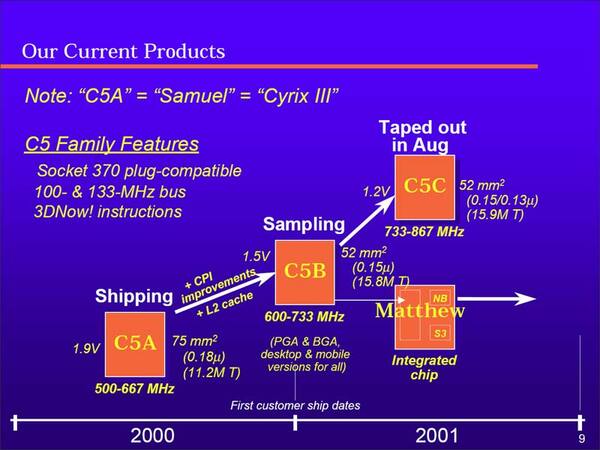

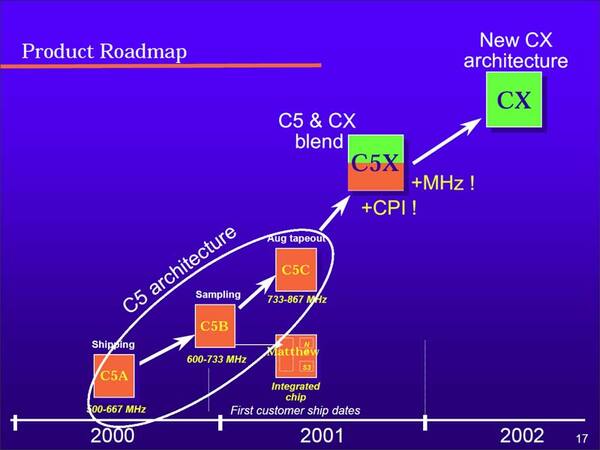

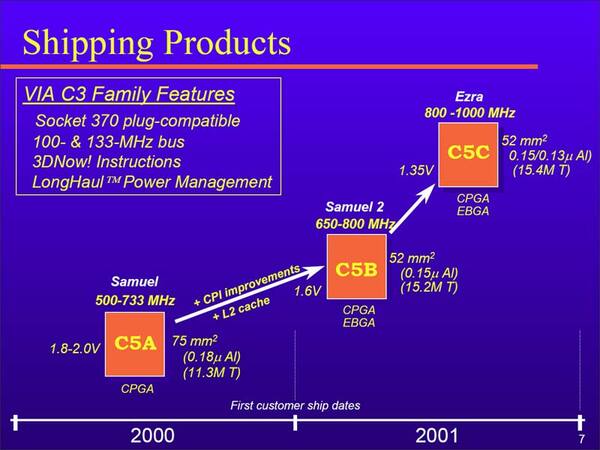

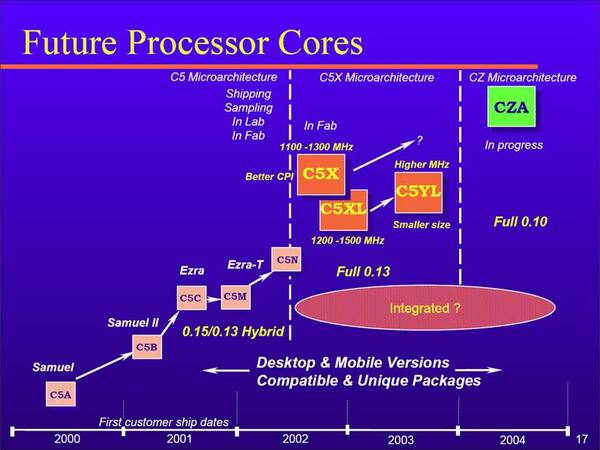

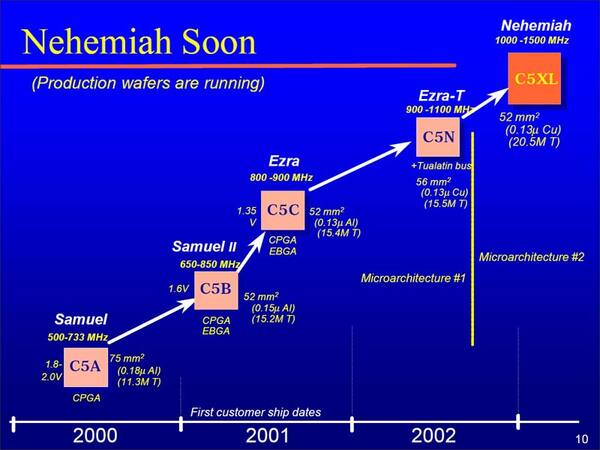

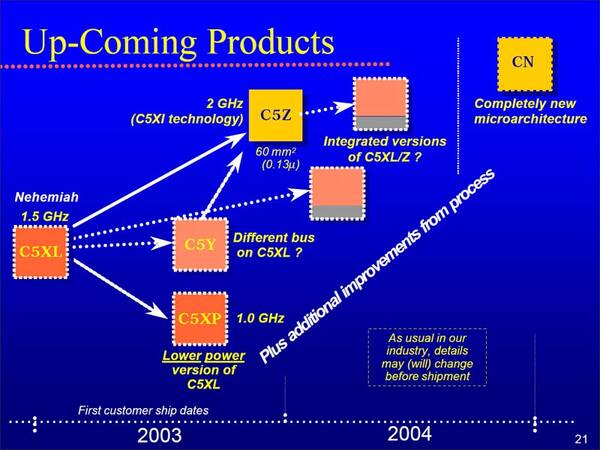

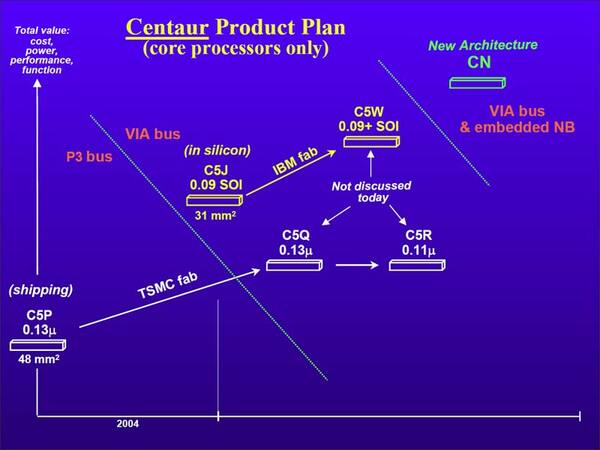

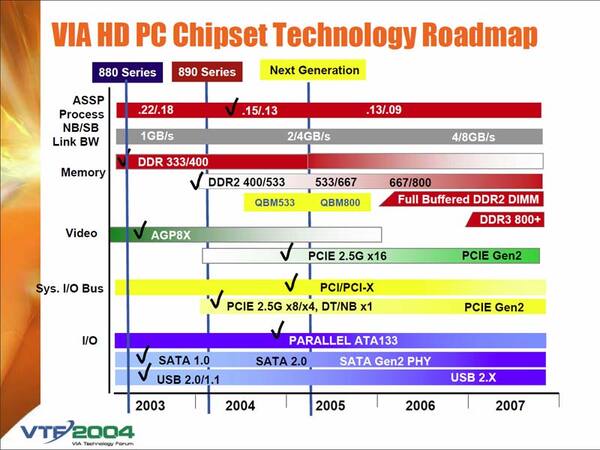

製品投入のペースはともかく、開発計画そのものはかなり意欲的である。1998年から2004年まで、ヘンリー氏は毎年半導体関連学会「MicroProcessor Forum」(MPF)で製品を発表しており、これらの際にロードマップがいろいろ紹介された。ちょっと多いが、以下にそれを示そう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ