特許訴訟と和解の関係で

C3系を2003年で打ち止め

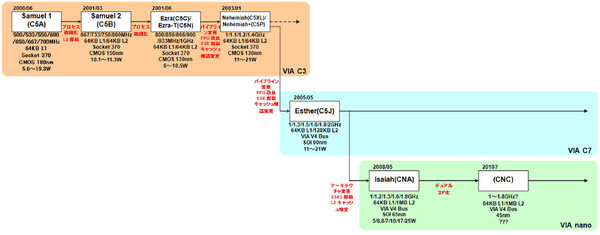

C5XLやC5PのNehemiahコアは、1ページ目のスライド1で名前の挙がった統合型CPU「CoreFusionプロセッサー」のベースになるなど、広く使われた。また「C3-M」と呼ばれるモバイル向け製品などもラインナップされたが、VIA C3系はこのNehemiahで打ち止めとなる。

最大の理由は、インテルとVIAの特許侵害訴訟の和解条件に関係する。2001年9月にインテルがVIAを訴えた事で始まったこの訴訟は、2003年4月に和解を迎えたが、その和解条件の中に「インテルはVIAに対して、インテルのプロセッサーバスと互換性のあるチップセットの製造・販売に対して4年間ライセンスを供与すると共に、5年目に関しても特許を主張しない」(プレスリリース)というものがあった。これにより、VIAは2007年まではSocket 370のチップセットを製造・販売可能だが、その先はできなくなる事になったからだ。

そのため、CentaurはP4バス(厳密にはPentium Mに使われたバス)をベースに、いくつかの変更を加えた「VIA V4 Bus」を新たに制定する。スライド8で「VIA bus」と書かれているのが、このV4 Busのことである。

ただし、いきなり2007年に全面的に切り替えるというのは間に合わないし、実のところ2003年頃からVIAの互換チップセットビジネスはかなり低調になりつつあり、2004年頃にはスライド9のようなロードマップが公開されはしたものの、事実上新製品はこの後登場していない。

Edenで急速に成長した

VIAの組み込み向けビジネス

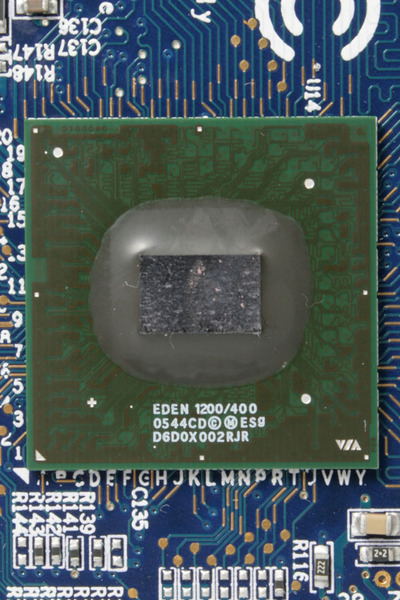

その代わりというわけではないが、VIAのEmbedded(組み込み)部門が急速に盛り上がっていた。特に同社が2001年に発表した、Mini-ITXフォームファクターに合わせたVIA「Eden」シリーズのSBC(Single Board Computer)の売れ行きが好調で、パソコン向け以外で急速に普及していた。

なにしろ、チップセットの場合は1組10~20ドル程度、CPUも40~50ドル程度の価格で、利益で言えばCPUとチップセットをあわせても数ドル程度なのが、SBCでは価格が1台100ドル程度で、利益もいきなり数10ドルになる。端的に言えば、出荷数量が1桁減っても売り上げや利益は変わらない事になる。

こうした状況を考えると、早めに独自バスに移行しても別に不都合はないし、無用な争いがインテルとの間で巻き起こる心配もなくなる。そんな事情もあって、2005年にはV4 Busに対応した「C5J」(Esther)コアが、「VIA C7」というブランド名で発表されることになる。

このC5J、流れからするとC5アーキテクチャーの延長線上にある。違いとしては、まず米IBMの90nmプロセスに移行することで微細化を図り、トランジスター数にゆとりができたため2次キャッシュを128KBに増量。また新機能としてSSE2/SSE3に対応したほか、暗号化処理アクセラレーターを内蔵している。

ダイサイズは31.7mm2とかなり小型化したが、これはちょっと特例らしい。というのも、MPF 2003でC5XL/C5Pが発表された際にヘンリー氏は、「トータルコストではダイサイズが50mm2程度がベストバランスになる」と述べていたのだ。

なぜかと言うと、CPUダイからは多数の配線が出ており、これをパッケージと結合するのだが、あまり小さいと配線に必要なボンディング(配線の接続部)が通常のものでは収まりきらない。すると、よりピッチの狭いものを使わなければならないのだが、これが非常に高コストになるからだ、という話であった。

実は同じような話は、ごく最近のAtomでもある。インテルのAtom Zシリーズで使われているパッケージは、下手をするとダイそのものよりもコストが高くつくという。こちらは省スペースが最優先の製品だから、多少コストが上がっても支障はないのだろうが、VIAの様に低コストのCPUを狙う場合、単にダイエリアを削るだけでは、パッケージコストが上がって意味がない。その意味では、次世代製品となる「Nano」プロセッサー(後述)が60mm2を超えるダイサイズになったため、再びコストは下がっているだろうと予想される。

では逆に、なぜC5Jでダイサイズが30mm2台まで縮小しまったのか? それは、例えば余裕を生かして大量の2次キャッシュを搭載しても性能がそれほど上がらないのに対し、トランジスターが増えることでリーク電流に起因する静的な(スタティック)消費電力も増えて、低消費電力性を維持するのが難しくなるからである。ダイサイズは大きくしたいが、そのために搭載すべき機能や回路がない、というわけだ。

それでもC5Jでは、最大2GHzまで動作周波数は伸び、また低消費電力のULV版(Ultra Low Voltage、超低電圧版)をラインナップするなど、製品ポートフォリオはずいぶん増えることになった。C3に変わるスタンダードなCPUコアとして、VIA C7は今後もラインナップされ続けると予想される。特にネットブックの急速な盛り上がりはC7にとっても明らかに追い風になっており、これにより低価格ノート向けのシェアも若干増えた模様だ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ