2000年代前半はSamuelコアとその改良版を投入

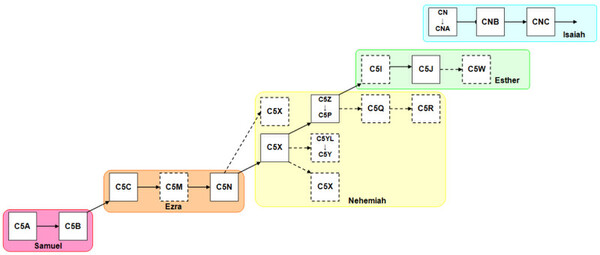

2004年を最後に、CentaurがMicroProcessor Forumに参加することはなくなってしまった。その代わりに、何がしかのプレゼンテーションが示されるVTFでも、将来ロードマップについては語られなくなってしまったが、これらの情報をまとめたのが以下の図である。「Samuel」「Ezra」というのはVIAの、「C5xx」「CNx」というのはCentaurでのコード名である。

当初は「VIA Cyrix III」として登場した「Samuel」から、次世代の「Ezra」コアまでは順調に推移した。しかし、その先の「Nehemiah」コア世代では、いろいろなプランが出ては消え出ては消えしていたことがわかる。最終的にこれが「Esther」コアに移行したものの、従来とまったく関わりを持たない「Isaiah」コアが登場している。ちなみにIsaiah(CN)が設計に入ったのは2003~2004年頃と思われ、設計開始から製品登場まで4~5年とそれなりの期間を要しているのは、インテルやAMDと同じである。

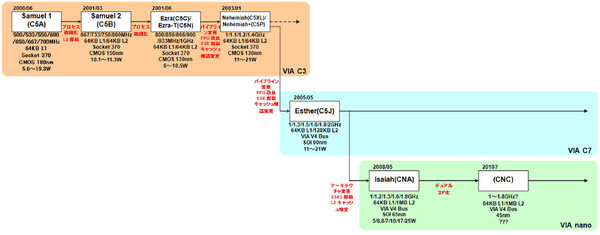

もう少し細かく説明しよう。まず、2000年6月に登場したCyrix IIIこと「C5A」の後を追い、150nm(0.15μm)プロセスを利用した「C5B」が2001年3月にリリースされる。製品名は「VIA C3」に変更され、動作周波数も800MHzまで引き上げられた。また、このC5Bコアをモバイル向けに低消費電力化したシリーズも登場した。こちらは300MHz駆動で最大2.5W、600MHz駆動では最大6Wと、最近のネットブック/MIDにも使えそうな低消費電力に収まっている。

これに続くのが、Erzaコアの「C5C」「C5N」である。C5CとC5Nの違いはバスとプロセスだ。まずバスだが、C5NはインテルのPentiumIII(Tualatinコア)でサポートされた、特殊なP6バスに対応している。

プロセスについてはちょっと説明が必要だろう。C5Cのプロセスは、トランジスターが130nm相当で、配線は150nmのアルミニウム(Al)配線という混載プロセスだった。というのはこの当時、製造会社の台湾TSMC社は、130nmの銅(Cu)配線プロセスでの量産を開始したものの、これがトラブル続きでまともに製造できないという事態に陥った。

余談だが、これに見事にはまったのが米Transmeta社だ。モバイル向けCPU「Crusoe」の第2世代製品は丸1年出荷が遅れ、それが最終的にTransmetaの消滅につながった。もっともTransmetaの場合はTSMCだけが悪いわけではなく、双方に問題があった模様だ。

話を戻すと、Centaurはトランジスターだけを130nmとし、配線は従来の150nm Al配線を使うことで、このトラブルに巻き込まれずに、特に問題なく製品を出荷できた。ただし、例えばスライド6を見ればわかるとおり、動作周波数こそ若干高速になったものの、ダイサイズは52mm2のまま変わっていない。

最終的に、C5Nでは130nm Cu配線を使うように変更されたが、配線設計のやり直しまでには至っていないのか、サイズはほとんど変わっていない。動作周波数の向上と消費電力低減の効果はあり、C5Nでは1GHzの大台に到達し、しかも最大消費電力は18.5Wとかなり低めに抑えられている。

C5X/XLで構造面でも拡張を施す

これに続き、2003年1月にリリースされたNehemiahコア世代の「C5XL」と、この改良型である「C5P」が、VIA C3の最終製品となった。そもそもC5XLとは、スライド5にある「C5X」の“Light版”である。

ではそのC5XはどんなCPUになる予定だったのか。2命令解釈のデコーダーと同時1.5命令(制限付きの同時2命令で実質1.5相当)の整数演算ユニット、2重化されたMMX/SSEの実行ユニットを持ち、64KBの1次(L1)命令/データキャッシュと256KBの2次(L2)キャッシュを搭載するというものだった。

C5XLはこれをスリム化したもので、1次キャッシュはC5X同様に命令/データ各64KBながら、2次キャッシュも64KB、デコード/実行ユニットも同時1命令のみとされたものだ。結果から言うと、VIAのターゲットしているバリュー・組み込み向け市場では、「まだ同時2命令実行のコアは高コスト過ぎる」ということで見送りになり、C5XLのみが生き残った。

こうした理由で、C5X/XLの内部構造はC5Nまでとは多少異なっている。パイプライン段数は12段→16段になり、FPU(浮動小数点演算ユニット)の高速化のほか(C5A~C5NまでFPUは動作周波数の半分の速度だったが、これを等速化)、AMDのマルチメディア命令セット「3DNow!」のサポートを取りやめ、代わりにインテルのSSEをサポートした。また2次キャッシュは容量こそ64KBと変わらないものの、4ウェイセットアソシエイティブ(キャッシュの方式)を16ウェイに変更してヒット率を向上させるなど、細かく変更している。

このC5XLは2003年11月に1GHz品が登場し、最終的に1.4GHzまで動作周波数をあげている。また、このC5XLをより低電圧で動作できるようにすると共に、若干の機能追加(乱数発生器を1→2に増加など)しているが、基本的にはマイナーチェンジである。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ