ロードマップでわかる!当世プロセッサー事情 第629回

Intel Architecture Day 2021で発表された11のテーマ インテル CPUロードマップ

2021年08月23日 12時00分更新

Sapphire Rapids

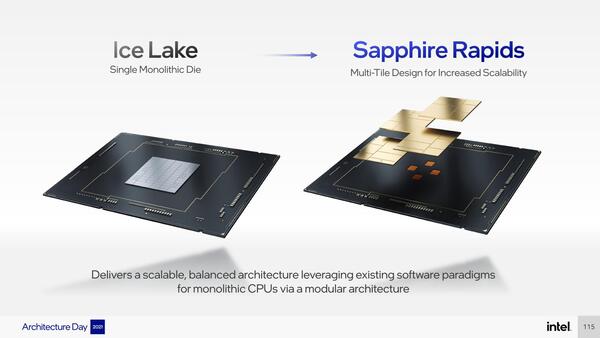

Sapphire Rapids、連載586回で推定図を紹介したが、構成的にはこれとあまり変わらないものが出てきた。

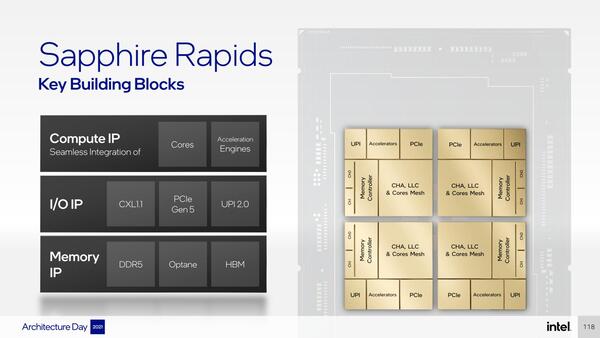

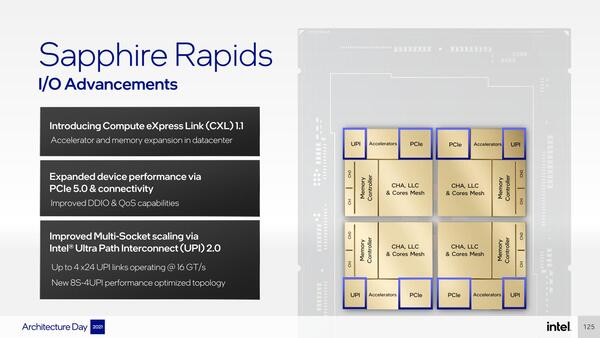

現時点でコア数などは不明のままだが、それぞれのダイにコアとメモリーコントローラー、UPI/PCIe、それとアクセラレーターが搭載される格好になる。

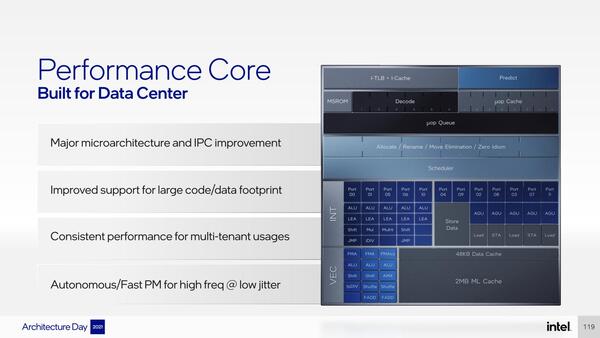

コアそのものはP-Coreだが、Alder LakeはL2(ML:Mid Level)キャッシュが1.25MBなのに対してSapphire Rapidsは2MBに増量されているほか、大きな違いとしてAVX512が実装されている。

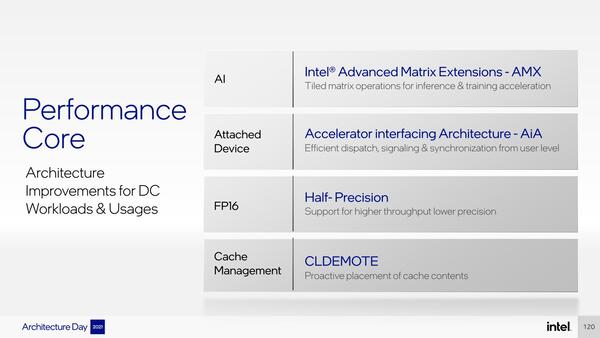

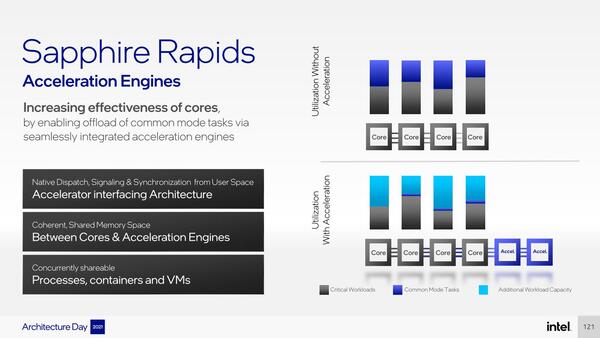

その他特徴として、AMXを含むアクセラレーター拡張機能(AiA:Accelerator interface Architecture)なるものが実装され、またAVX512はFP16がサポートされるなど、いくつかのサーバー向け拡張機能が有効化されている。

Sapphire Rapidsではまた、AMX以外にIPU(Infrastructure Processing Unit)も実装されている。IPUは今年6月に発表されたもので、現時点で具体的な話は出てきていないのだが、これをSapphire Rapidsに搭載すると、定型処理に関してCPUからオフロードすることで、CPUをメインの処理により専念させられる。

IPUで一番わかりやすいのが、例えばTCPのオフロードである。今まではイーサネットカードにこれを搭載していた(今後も搭載される予定だ)が、それとは別にこうしたものを処理する専用コプロセッサー(というよりアクセラレーター)を載せた

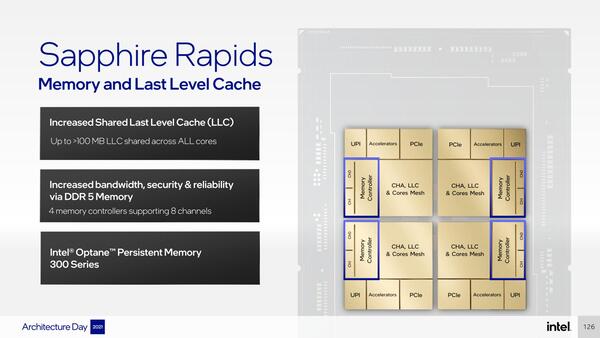

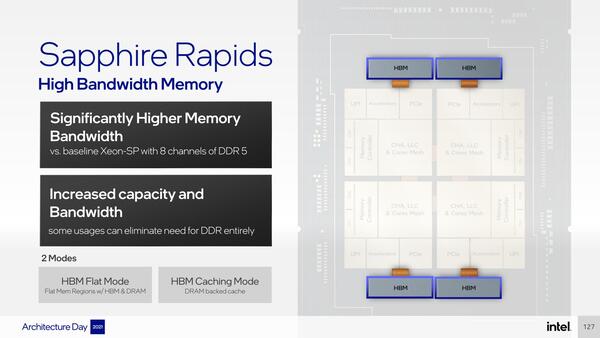

I/Fとしては、UPIが4組とPCIe 5.0/CXL 1.1が実装されることが発表された。またメモリーコントローラーはダイあたり2chのDDRなのは想定通り。HBMに関してはメモリーコントローラーとは別の場所につながっているが、これは単にこれは図版の問題であって、実際はメモリーコントローラーにつながっているものと考えられる。

I/FのUPIが4組なのは筆者の想定通り。ただ、Sapphire Rapidsの内部構成図で斜め方向のリンクはなかった。それはともかく、1組あたり24レーンというのがよくわからない。このあたりもHotChipsで解説を期待したいところだ

なお、連載623回で、Knights LandingではMCDRAMとDDR3の組み合わせに3種類のモードがあることを説明したが、Sapphire RapidsではHybrid Modeは省かれ、Flat ModeとCacing Modeの2種類だけが提供されるそうだ。

| MCDRAMのモード | ||||||

|---|---|---|---|---|---|---|

| Cache Mode | DDR4メモリーのキャッシュとして使う | |||||

| Flat Mode | MCDRAMもメモリーの一部として扱う | |||||

| Hybrid Mode | MCDRAMの一部をキャッシュに割り当て、残りをメモリーの一部として扱う | |||||

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ