ロードマップでわかる!当世プロセッサー事情 第632回

Intel 7とTSMC N5で構成されるHPC向けGPUのPonte Vecchio インテル GPUロードマップ

2021年09月13日 12時00分更新

過去3回に引き続きインテル新製品の詳細をお伝えする。今回はPonte Vecchioについてだ。

実はPonte Vecchioもやはり新しい話はHotChips 33のカンファレンスセッションでは出てこなかった。ということで、実はあまり新情報はなかったりする。大まかな話は連載629回で説明した通りだが、一応復習も兼ねて簡単に説明しよう。

EUあたりの性能が倍増した代わりにEUの数が半減

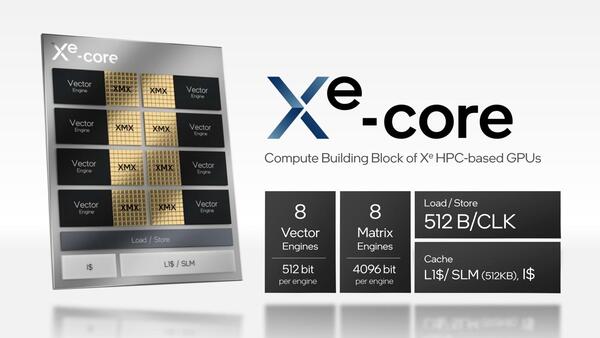

Xe-HPC、つまりPonte Vecchioの演算の最小単位はXe-coreとなるが、同じ名前ながらXe-HPG(GPU)向けとは若干構造が違う、というのは以前触れた通り。1つのXe-coreに8つのVector Engineと8つのMatrix Engineから構成される。

Ponte VecchioのXe-core。XMXの方は1サイクルあたり4096bitの演算が可能だが、Load/Storeが間に合っていないあたり、行列演算などを本格的にやる実装にはなっていない気がする

Vector EngineというのはこれまでEU(Execution Unit)として説明されていたもので、中身は8-wideのFPU/INTの巨大なSIMD Engineである。ただ同じXeでもXe-LPのEUは、1サイクルあたり256bit演算になっていたのが、Xe-HPCでは上の画像にもあるように演算器の幅が512bitに倍増している。

つまりXe-LPやXe-HPG向けでは256bit幅のEU×2(ただしスレッドコントロールは共通)という構成だったのを、Xe-HPC向けでは512bit幅のEU×1として扱う格好に変更したようだ。したがって、同じEU(上の画像の表現ではVector Engine)あたりの性能が倍増して、ただしEUの数が半減するという形になっている。

この理由であるが、おそらくはAVX512やAMXなどとの連携を考えると、512bit幅のデータ型を扱えるようにするのが得策と考えたからだろう。Xe-CoreにはこのVector Engineが8つあるから、これにあわせてLoad/Storeユニットも512Bytes/サイクルに強化されている。

一方のMatrix Engineであるが、これは連載579回で説明したDP4A命令を処理するのが主眼と思われる。ひょっとしてAMX命令を処理できるのか? と思ったが、どうもそうした構造にはなっていないようだ。ちなみにDP4A命令そのものはVNNI命令と互換性があるそうで、ただしx64コアよりも大幅に高速化されている格好だ。

インテルの説明によれば、OpenVINO 2021.1 release以降ではこのDP4A命令をサポートしているということで、つまりx64でもVNNIを利用してDot Products演算を高速に処理できるが、XMXを利用するとプログラムをそのままでさらに高速化できることになる。位置付け的にはNVIDIAのVolta以降で実装されたTensor Coreと同じ形である。

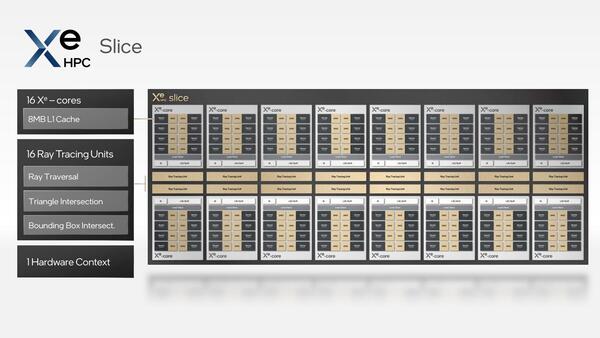

Xe-Coreを8つ集積したSliceが

最小の演算単位になる

さて、Xe-HPCを構成する最小の演算単位は、このXe-Coreを8つ集積したSliceとなる。

Xe-HPGと比べると、Xe-HPGはXe-Core×4で1つのRender Sliceを構築するのに対し、Xe-HPCはXe-Core×8で1 Sliceとなる。

そして、Xe-HPGは、2 Vector Core単位でThread Dispatcherが実装されており、Xe-Coreあたり同時8スレッド、1 Render Sliceあたりで言えば32スレッドが同時に動く(In-Flight状態のスレッドは当然さらに多いと思われるが、インテルはまだ1つのXe-Coreでハンドリングできるスレッドの数を公開していない)のに対し、Xe-HPCではSliceあたりで1つのHardware Contextとしており、同時に実行できるスレッドの数は1つとなる。相当粒度の低い構成になるわけだが、逆にピーク性能を高めようとするとこうした構成の方が効果的なのかもしれない。

さらに言えば、上の画像には記載されていないが、Xe-HPCではここに外付けの形で2次キャッシュが実装可能である。Xe-HPGも2次キャッシュはサポートするが、こちらはモノリシック構造で提供されるようで、このあたりも違いと言えるだろう。

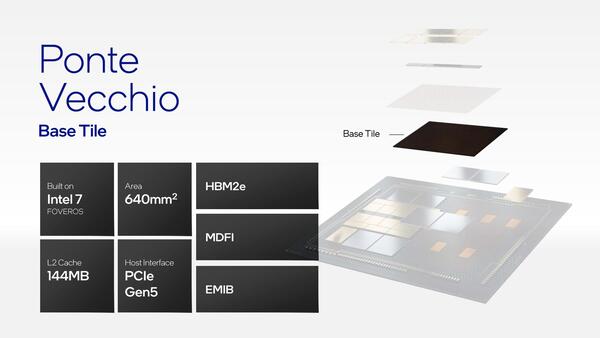

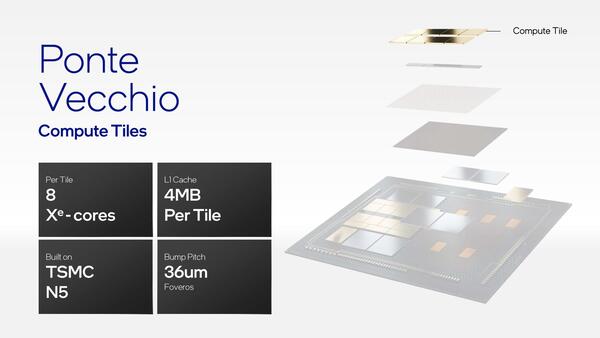

ところで2020年のArchitecture Dayでは、Ponte VecchioはBase Tileが10nm SuperFin、Computeが次世代プロセス、Rambo Cacheが10nm Enhanced SuperFin、Xe-LinkがExternalとなっていたが、今回Compute TileはTSMC N5、Base TileはIntel 7とされている。

つまり2020年の時点では旧10nm SuperFinでBase Tileを製造予定だったのが、10nm Enhanced SuperFinに切り替わった格好だ。Xe-LinkはTSMC N7で最大90Gの速度とあるが、これはおそらくレーン全体での話で、1レーンで90Gという話ではないと思われる。

Compute TileはTSMC N5とある。これはもともと“Intel Next Gen & External”となっていたので不思議ではない。今のスケジュールでIntel 4を使うと、量産開始が2023年になってしまうからだ

ちなみに性能という観点では、Ponte Vecchioが1つでFP32/FP64が45TFlopsという数字はすでに示した。インテルは、「これはA0シリコンでの数字だ」としており、今後もう少し動作周波数が上がることを示唆していたが、HotChipsの説明ではこのほか、ResNet-50を動作させてInference(推論)が43000イメージ/秒以上、Training(学習)で3400イメージ/秒以上という数字も公開された。

この数字、比較するものが古いが、Inferenceで言えばインテルが買収したHabana LabsのGoyaが1万5000そこそこなので、これを軽く2倍以上上回る性能ということになる。Trainingも、Gaudiの性能がおおむね1600イメージ/秒とされていたので、これもやはり2倍以上である。

こうなると、Habana Labsを約20億ドルで買収して入手したGaudiとGoyaの存在価値が問われかねない気もするのだが、どうするつもりなのだろうか?

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ