前回のA64FXに続き、ARMプロセッサーの後編はAppleのMac(Macintosh)向けApple Siliconの話である。が、いきなりここに飛びつく前に、まずは過去の経緯を簡単に振り返っていこう。

何度もアーキテクチャー変更があった

Macのプロセッサー遍歴

冒頭に書いておくと、Macがプロセッサーアーキテクチャーを変更するのは、公式にはこれで3度目。非公式には4度目になる。

つまり初代のMacintoshやMacintosh II、Quadraなどに使われてきたMC68Kシリーズ、PowerMacに移行が決まる前に、非公式に移植が進められてきていたMC88K、そしてPowerPC、x86ときて、今回がARM v8-Aである。

MC88Kがあまり知られていないのは、製品が出ていないのだから当然であるが、68K→88Kのエミュレーターが完成した段階で、MC88KからPowerPCの乗り換えが社内でアナウンスされたそうで、移植担当者が相当なげいたという話を聞いたことがあるが、それはそうであろう。

初期のPowerPCのプロセッサーバスは俗に601 Busと呼ばれるが、これはMC88100との互換性を持つものだった。理由は、連載500回で述べたが、88K→PowerPCへの移行を容易にするためである。このあたりの話は以前「忘れ去られたCPU黒歴史」のMC88000の章(単行本化の際に加筆した章なのでウェブでは未公開)で触れた話だ。

iPhone/iPad向けSoCはARMコアを採用

話を戻すと、今度は“Apple製のシリコン”を搭載するというわけで、iPhone/iPadに利用されているARMベースになるのは間違いない。開発キットにはA12Z Bionicが搭載されているほどだから、これでARM以外だったらその方がどうかしている。

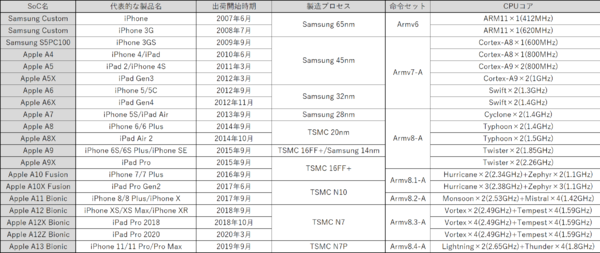

さて、ではAppleのARMとの関わり合いは? ということでiPhone/iPad向けSoCを一覧で示してみたのが下表である。

初期はSamsungのカスタムSoCを利用しており、これはオーダーをAppleからSamsungに投げ、それをもとにSamsungが組み上げた格好だ。これがAppleの設計に切り替わるのは、Apple A4からである。

Apple A5以降はiPhone向けのAn(n:5~13)と、iPad向けのAnX(n:5~12)に分かれているが、基本的にiPad向けはエリアサイズと消費電力にゆとりがある(筐体が大きいので、パッケージサイズが大きくても許容されるし、また放熱能力とバッテリー容量にゆとりがあるから、消費電力が上がっても許容される)ので、iPhone向けのAnシリーズのコア数を増やしたり、動作周波数を引き上げたりした派生型と考えればいい。

さてその基本のAnシリーズだが、A5まではARM提供のIPコアを利用していたが、A6以降は独自設計のコアを利用しており、Swift/Cyclone/Typhoon/Twisterと来て、A10世代からはbig.LITTEに基づくBigコア(Hurricane/Monsoon/Vortex/Lightning)とLittleコア(Zephyr/Mistral/Tempest/Tunder)の両方が利用されるようになっている。

この独自設計のコアであるが、Appleは2008年にP.A.Semiという会社を買収しており、ここの設計チームがそのままAppleの独自コア開発に携わる、と当時から噂されていた。

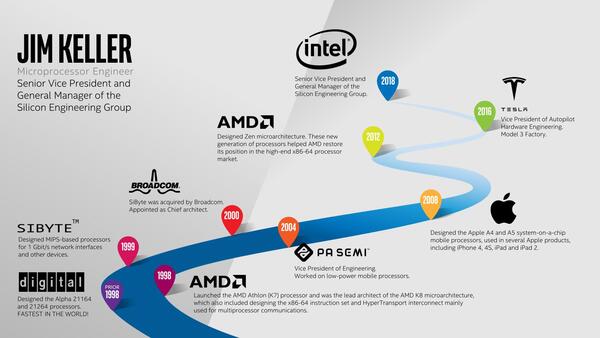

このP.A.Semi(元はPalo Alto Semiconductor)は2005年のFall Processor ForumでPA6TというPowerPCベースのコアと、これを実装したPWRficient 1682MというSoCを発表しているが、この発表者が誰あろうJim Keller氏(当時の肩書はVP Engineering, Architecture Group)である。

最近ではインテルを辞任したことで話題になったKeller氏であるが、そのインテルがKeller氏就任直後に出したのがこちら。

このスライドで、Keller氏はAppleでA4とA5の開発に携わったとしている。時期的に言って嘘ではないが、実際にはもっと重要な、A6/A7のグランドデザイン(というか移植)にめどがついたことでAppleを離職したのではないかと考えている。

というのは、表からもわかるようにApple A4/A5はCortex-A8/Cortex-A9をベースとしたシステムで、もちろんこれをベースにSoCを組み上げるためにはPWRficient 1682Mや、さらにその前のSiByteのSB1000での経験と知識が大いに役立ったと思うのだが、Keller氏の本職(?)はCPUアーキテクトであり、CPUコアそのものはいじれないCortex-A8/A9を組み上げるのは、別に氏でなくても足りる。

しかしこれに続く独自コアのSwift/Cycloneは、CPUアーキテクトなしではどうにもならない。こう考える理由は、PA6Tというコアの先進性にある。

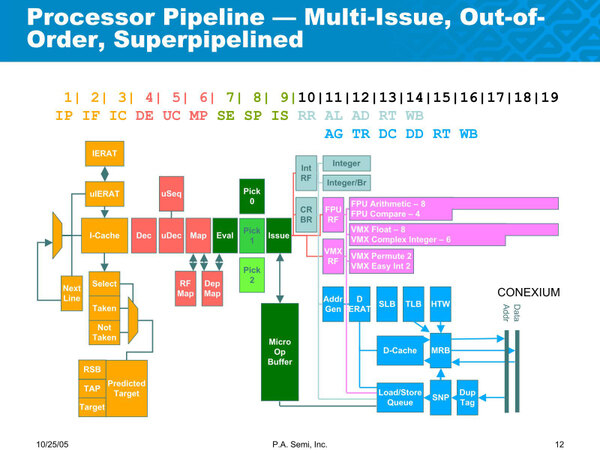

PA6T。フロントエンドは4命令/サイクルでフェッチ(読み出し)し、これを1サイクルあたり3つの内部命令に変換、それぞれ実行する。発行ポートは整数演算、FPU/VMX演算、Load/Storeの3つ

画像の出典は、P.A.Semiの“A Power-Efficient, Scalable Processor Family”の講演スライド

PA6Tは、命令セットこそPowerPC 2.04準拠ながら以下の重厚な構成である。

- 32bit/64bit両対応。FPU及びVMX SIMDも実装

- 4命令フェッチ/3命令同時発行のアウト・オブ・オーダー/スーパースカラー実装

- MicroOpを利用し、さらにMicroOp Buffer(L0 Cache)まで搭載

このような構成でありながら、65nmプロセスでの製造で2GHz駆動のコアあたりの消費電力は6.25W(同社の説明は「8コアで50W以下」であった)という高効率性を誇る。

2GHzにおけるSPECint(おそらくSPEC CPU2000のことと思われる)は1000以上、というのが説明であった。ちなみにSPEC CPU2000で1コアのスコアが1000前後というのは、例えばDellのPowerEdge 1750にあたり、PrestoniaベースのXeon 3.06GHz(533MHz FSB)相当ということになる。

ここからは筆者の推測だが、Keller氏は「副業として」Apple A4/A5の開発の面倒も見ていたかもしれないが、本職はこのPA6Tのアーキテクチャーをベースに、新規にARMコアを起こす作業を、(買収にともなう)2008年のAppleの入社から、2012年の退社までの間に携わってきたのではないかと考えている。

もともとのPA6Tは64bit対応のアーキテクチャーなので、本命はARM V8-AのCycloneである。ただ64bit対応のためにはiOSやアプリケーションの移行も同時に必要である。したがって、まずは前段階として32bitのARM V7-Aを移植したSwiftをリリース、次いでこれにARM V8-Aを追加したCycloneを開発したことになるだろう。

実際には、フロントエンドはPowerPCからARMへの命令セットの変換になるが、バックエンドはアプリケーションにもう少し最適化した形での実行ユニットの強化が行なわれたと思われる。

特にPA6Tの場合は65nmプロセスを使い、消費電力もコアあたり6W程度がターゲットだったので、複雑なユニットを同時に動かすよりも、シンプルなバックエンドを動作周波数を上げて動かす方が効率的かもしれないが、iPhone向けだとコアあたり1W程度に抑える必要があるため動作周波数が上げにくい。

その代わりに利用できるトランジスタ数が大幅に増える(Samsungの28nm HKMGプロセスやTSMCの20nmプロセスがターゲット)ので、自ずと構成そのものも見直す必要があるだろうし、実際見直したはずだ。こうした実装の指揮こそ、Keller氏の肩書にふさわしい作業と言える。

もっとも、Keller氏がAppleを離れたあとも、Appleのプロセッサー開発は当然続く。どこまでKeller氏の影響があったかははっきりしないが、Cycloneどまりか、あっても続くTyphoon/Twisterまであたりでであり、big.LITTLEに対応したHurricane以降はおそらくもうKeller氏の作業はあまり関係なくなっているだろうと想像される。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ