前回に続き、Data Center and AI Technologyで判明した情報をお伝えしよう。このイベントの一番最後で、AMDはInstinct MI300に関しての詳細を発表した。といっても肝心の性能や内部構造などは今回は見送りである。ではなにが明らかになったか? というと、パッケージ構造の詳細である。

Instinct MI300Xを新たに発表

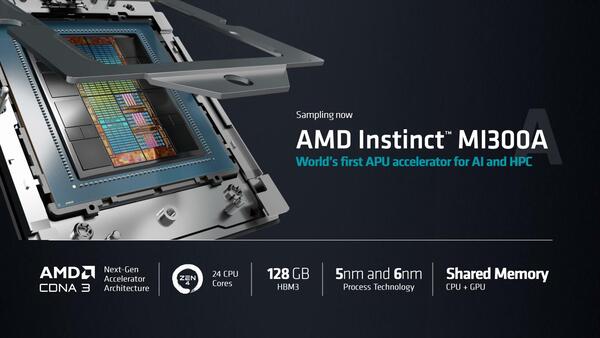

Instinct MI300シリーズは今年のCESで公開されたわけだが、この時公開されたのは以下の情報だ。

今回発表されたのは以下のとおり。

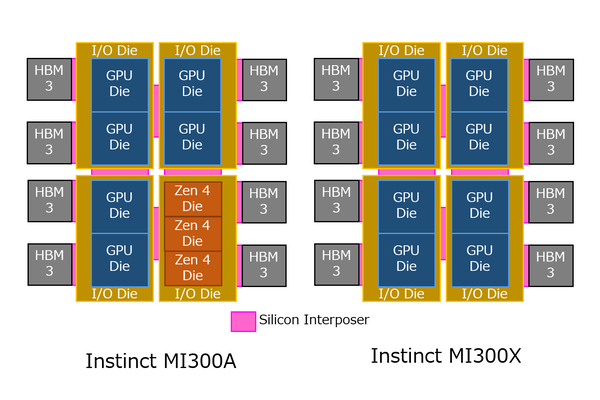

- APUはInstinct MI300Aという名称で、前情報の通り24コアのZen 4とGPUを搭載する。3Dチップレット構造で、合計13チップレット。

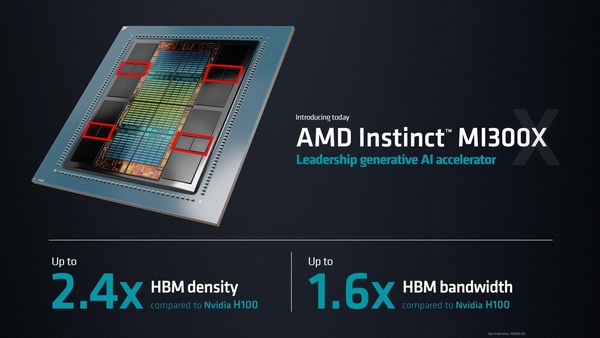

- MI300Aとは別に、CPUを持たないInstinct MI300Xが今回発表された。こちらはHBM 3をMI300Aの16GB×8から24GB×8構成に変更、搭載メモリー量は192GB/秒に達する。同じく3Dチップレットで、合計12チップレット。

性能に関して言えば、今回はとにかくInstinct MI300Xの192GBという搭載メモリー量とメモリー帯域を前面に押し出した格好で、具体的な性能などは一切開示されていない。

ということで以下は筆者の分析である。まず物理構造。そもそも上の画像を見ても、HBM 3の間に謎の小さなダイが存在する。これはなんだ? ということでSam Naffziger氏(SVP, Corporate Fellow and Product Technology Architect)に「これがHBM 3のメモリーコントローラー?」と聞いたところ「違う」とのこと。これは単に高さを合わせるためのサポーターであって、チップレットの数には入っていない、という返事であった。

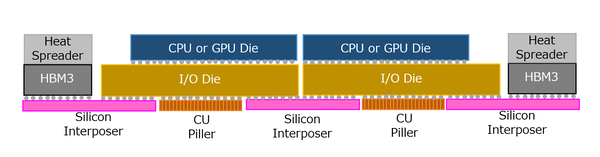

ということで、下図が上から見た構造図、さらにその下が横から見た構造図である。

「I/Oダイ同士やHBM3はシリコン・インターポーザーで接続される」というのがNaffziger氏の説明で、ということは図のように3層構造になっているわけだ(ここでシリコン・インターポーザーの間に挟まれるCU Piller(銅柱)というのは、Instinct MI200で採用されたElevated Fanout Bridge 2.5Dに出てくる部分だ。

インテルのEMIBと異なり、パッケージそのものを掘り下げるのでなく、シリコン・インターポーザーの周囲を銅柱で持ち上げることで高さのつじつまを合わせる方式である。CPUおよびGPUダイはTSMC N5で、I/OダイはTSMC N6で製造される。このI/Oダイであるが、説明から判断すると以下を搭載する形となる。

- CPU/GPUとの接続(TSVを経由してのMicroBumpで接続と思うが、ひょっとするとSoIC方式の3D接続かもしれない)

- HBM 3のI/F

- インフィニティ・キャッシュ

- インフィニティ・ファブリックおよびPCI ExpressのI/F

インフィニティ・キャッシュに関しては後述するが、そもそもMI300のGPUダイにはほとんど2次キャッシュにあたる部分がない。連載693回のRDNA 3でも説明したが、TSMCのN7/N6とN5では、ロジック密度はともかくSRAM密度はほとんど変わらず、大容量SRAMを搭載するならN6の方がコストが下がって有利であり、またHBM3やインフィニティ・ファブリック/PCIeなどのPHYもN6の方が有利である。

したがって、これを別チップにするのは合理的だし、実際Navi 31ではそうなっているわけだが、Navi 31ではGCDとMCDを水平方向に並べたのに対し、MI300シリーズではこれを垂直に重ねたのが相違点である。

ここでHBM3の上にヒートスプレッダーが重なっているのがわかるが、そもそもHBM 3の高さはGPUやCPUのダイとそれほど変わらないので、I/OダイとCPU/GPUのダイを重ねると明らかに高さがマッチしない。そこで上にヒートスプレッダーを挟んで均一な高さになるように工夫していると思われる。

実はこう考えると、先ほどの画像にある赤枠のサポーターの意味も見えてくる。HBM 3にヒートスプレッダーを重ねただけでは、機械的強度はあまり期待できない。放熱の必要があるので、チップ全体のヒートスプレッダーに接触する必要はあるが、強い過重がかかった時に必要以上に力がかかりすぎるとHBM 3の破損の恐れがある。そこで必要以上の力がかかった時に、HBM 3の代わりに荷重を受け止めるのがこのサポーターなのだろう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ