日立製作所が取り組むCMOSアニーリングマシン&量子ゲート型のシリコン量子コンピューター

日立が取り組むシリコン量子コンピュータの優位性

もうひとつの取り組みが、量子ゲート型のシリコン量子コンピュータの開発である。

日立製作所では、2011年7月に、同社中央研究所において、新世代コンピューティングプロジェクトを発足。これが量子コンピュータに取り組むきっかけになっている。また、日立では、CMOS半導体回路技術を用いたシリコン量子コンピュータの実現に向けては、日立ケンブリッジ研究所を中心に研究開発を進めてきた経緯がある。

同社では、量子コンピュータでは、複雑な計算を解くために量子ビットを大規模に集積することが重要であり、そこにシリコン量子コンピュータは優位性を発揮できると見ている。

「シリコン半導体技術の特徴は、素子の微細化とともに、素子の高集積度であり、量子コンピュータの大規模化には、シリコン量子ビットアレイや、高精度制御・読み出し回路などの集積度を高めることが重要になる」とする。その上で、「従来は、量子ビット素子の完成度向上を重視し、量子ビットの数を徐々に増やしていく質を重視したボトムアップ的なアプローチを行っていた。だが、シリコンには、均一な特性の素子を、多数集積することが可能だという特徴がある。日立は、2018年から、シリコン半導体技術の優れた集積性を最大限に生かし、はじめから量を重視した量子コンピュータの開発アプローチへと変更し、質にアプローチするトップダウン方式を採用した。研究開発の手法をギアチェンジした」とする。

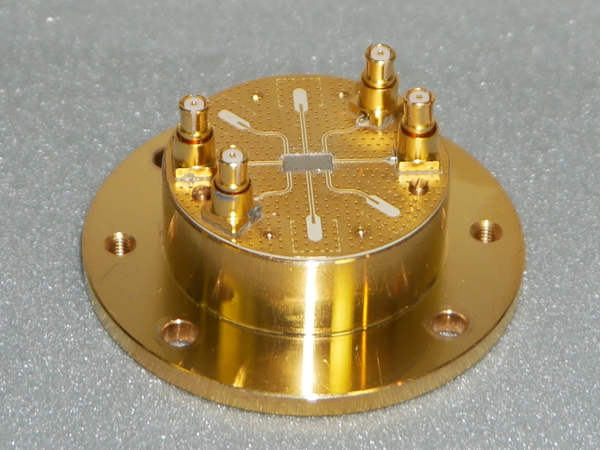

この取り組みをもとに、2020年には64量子ビットが形成可能な量子ビットアレイの基本構造の試作を行うことに成功した。従来、量子コンピュータは、大規模集積化に伴い、量子ビットを動作させるための信号配線数が増えることで小型化が困難だったが、同量子ビットアレイでは、CMOS半導体回路技術を応用し、複数の量子ビットを制御する信号配線を共通化することで、配線数の増加を抑制しながら量子ビットを2次元状に配列して大規模集積化を実現することができたという。

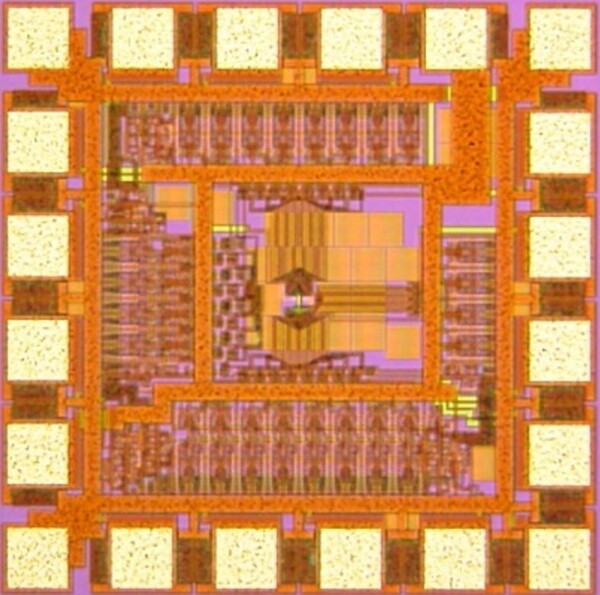

さらに、2021年9月には、研究成果として「Q-CMOSプロセス」を発表した。Q-CMOSプロセスでは、128個の量子ドットアレイと電子を制御するCMOS回路を同一チップに混載できるようにしており、高精度制御と読み出し回路、シリコン量子ビットアレイの集積度を高めることができ、これがシリコン量子コンピュータの実現に大きな一歩につながるとしている。

Q-CMOSプロセスでは、電子1個が格納された量子ドットを、アレイ上の所望の位置に安定的に形成できるようになり、さらにこれを制御できるようにすることで、量子ビットとして動作させることができる。シリコンの集積性を最大限に生かしたアプローチが可能になる技術が完成したといえる。