テクノロジーの肝はDNAコアではなく

DNAのシミュレーションが可能なMERAコンパイラにある

こうした構成では、あとはプログラミングが鍵になるわけで、ここに向けてEdgeCortixが提供するのがMERA(Multi-module efficient Reconfigurable Accelerator)コンパイラというツールである。

MERAがすごいのは、単に同社のDNAコアのみならずCPUやGPUに対応(CPUはLLVMを、GPUはCUDAやMetalをそれぞれ経由する)していることで、例えば実装の際のシミュレーションやデバッグはCPUやGPUを使い、本番はDNAコアという使い方もできるわけだ。

ある意味EdgeCortixのテクノロジーの肝は、DNAコアというよりもこのMERAの方にあるようで、それもあってあまり詳細が説明されていないが、DNAコアそのものはいろいろ割り切った構成とはいえ、なにか飛びぬけてすごいというものではなく、差別化はむしろこのMERAコンパイラの側でソフトウェア的に行なっており、これを最速で実行できるプラットフォームとしてDNAコアも提供している、という方が正確なのかもしれない。

グラフ分割あたりからMERA独自の部分が次第に増えていくようだ。インターコネクトはおそらく“Operator and Layer fusion”や“Tiling”の段である程度決まり、これを最終的に“Scheduling & Allocation”で確定させるのだろう

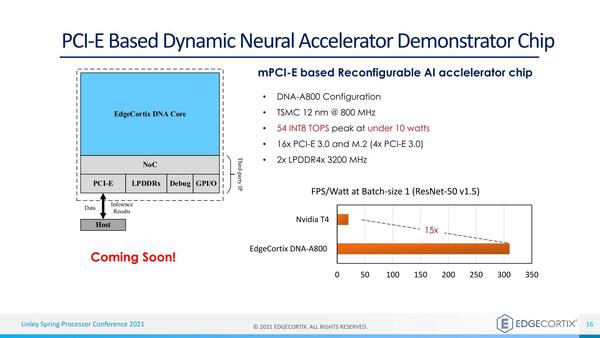

今年4月の時点では、54TOPsの性能を持つDNA-A800のASIC IPの提供開始とサンプルチップが「間もなく登場」という話であった。

実はEdgeCortixはこれに先立ち2020年2月にはXilinxのFPGA向けにDNA-F200というDNAコアのIPをすでに提供済みであり、また2020年10月にはFPGA上での動作デモも行なっている。

この時のデモとは違う映像だが、FPGAを利用して入力画像から顔認識と動き認識、分類をリアルタイムで行った動画がYouTubeに上がっているのでご覧いただくとわかりやすいだろう(撮影場所が秋葉原なのがおもしろい)。

ラインナップ的にはこのDNA-A800が最上位であり、下はA50からだんだん性能が良くなる形になっている。

シミュレーションによるLatencyやArea Efficiency、Power Efficiencyなども示され、またFPGAを使っての実機での性能比較も紹介されるなど、創業2年でよくここまでそろえたな、という感じになっている。

これは3種類のネットワークで1枚の入力画像を処理して結果が出てくるまでのレイテンシーを測定したもの。配線のReconfigurationを掛けると、1割弱レイテンシーが削減できる、というのがおもしろい

こちらは性能とエリアサイズ(おそらくTSMCの12nmをベースに試算したものだろう)を比較したもの。絶対的なエリアサイズが不明なのでなんともいい難いところはあるが、DNA-A050なら数平方mm程度に収められれば、ギリギリハイエンドMCUやローエンドMPUに組み合わせることも可能で、しかも性能は結構取れそうな感じだ

こちらが先に触れたDNA-F200 IPをXilinxのAlveo U50というFPGA搭載PCIeカードで実施した際のレイテンシー。DNA-F200は同社の第2世代IPで、第1世代(グラフ右端の2つ)に比べて性能が向上しているとする。で、DNA-Aシリーズは第3世代になるのだろうか?

ただ4月に“Coming Soon”と説明された実際のシリコンは、今のところまだ完成されていないようで、10月に開催されたLinley Fall Processor Forum 2021でも同社のホームページでもこれに関する発表がないのはやや気になるところだ。

10月時点でのEdgeCortixのエンジニアの数は日本と米国合わせて25名程、と少数精鋭を貫いており、この数のエンジニアでASIC製造まで手掛けるのはなかなか驚異的ではある。この規模の会社であれば会社の固定費はそう大きくはならないだろうとは思うが、その一方でIP売りという方向性はなかなか売り上げが立ちにくい部分もある。

この先、どこまでASICカスタマーをEdgeCortixが獲得できるのかが同社の存続の鍵を握るのは間違いないだけに、健闘してほしいところである。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ