16個のスライスに分割した

巨大な32768bit幅のSIMD

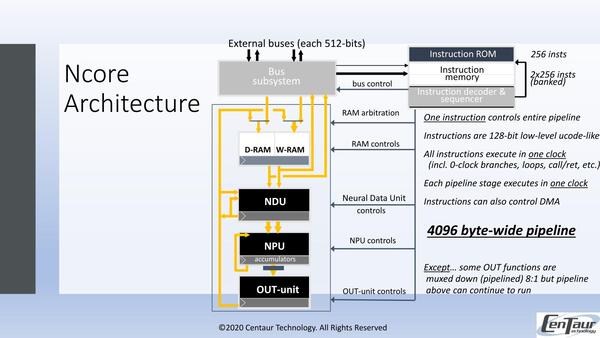

各々のスライス構造を示したのが下の画像である。

Ncoreのワークフロー

(0) Bus Subsystem経由でD-RAM(Data RAM)とW-RAM(Weight RAM:ネットワークの重みを格納する領域)にデータが格納される(これは処理パイプラインの外)

(1) NDU(Neural Data Unit)が4096Bytes分のデータとWeightを読み込み、これの並べ替えや回転、Edge Swap、あるいは前サイクルで処理の終わった出力画像の取り込みといった処理を1サイクルで実行する。

(2) NPU(Neural Processing Unit)で処理する。処理はMAC(乗加算)と加減算、最大/最小、論理命令その他をサポート。9bit/16bit整数とBFloat16が取り扱える。9bit整数ならMACが1サイクル、BFloat16でも3サイクルで処理できる。ちなみにデータ型そのものは8/16bit整数とBFloat16で、8bit整数は内部で9bit化して処理される。ここでWeightのデータを基に、データをネットワーク構造にあわせて処理する。

(3) OUT-unitでは、NPUの結果の量子化やReLU(ランプ関数)/Tanh/シグモイド関数を利用した活性化、出力の正規化などが行なわれ、結果がD-RAMないしNDUに引き渡される。ほとんどの処理は1~3サイクルで完了するが、例えば8:1の重ね合わせなどは最悪値で10サイクルほど要する

ここで1回分のデータ(例えば映像処理なら1フレーム分の画像データ)が完了するまで(1)~(3)をパイプライン式に繰り返し、終わったら(0)に戻る、という形である。

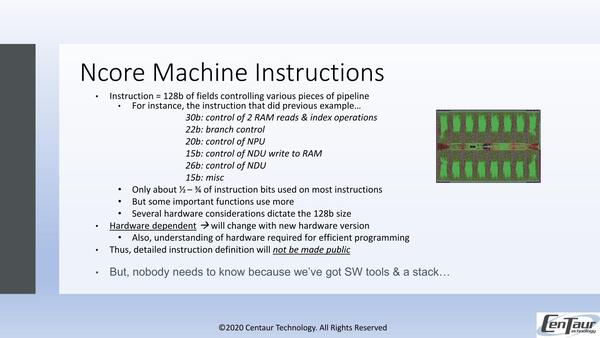

一方制御命令であるが、128bit幅のもので、これを見ると限りなくVLIWに似ている。ただし詳細は未公開である。

このあたりは昔のVIA C3などで提供されてきた独自拡張命令に近い感じに見える。ただ必要なツールやスタックはCentaurから提供されるので、直接アプリケーションプログラマーがこれを触る必要はない、としている。

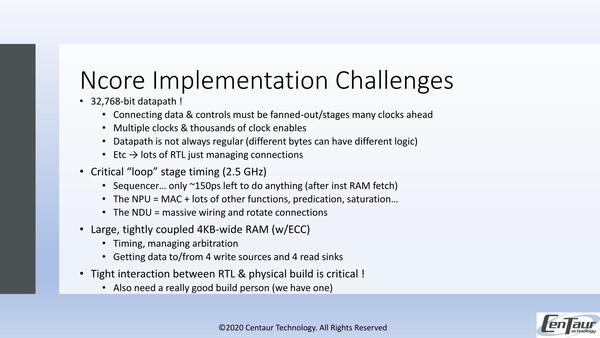

さてNcore、構造そのものはシンプルながら、なにしろ32Kbit幅のデータパスであるから、それなりに実装は困難だったらしい。

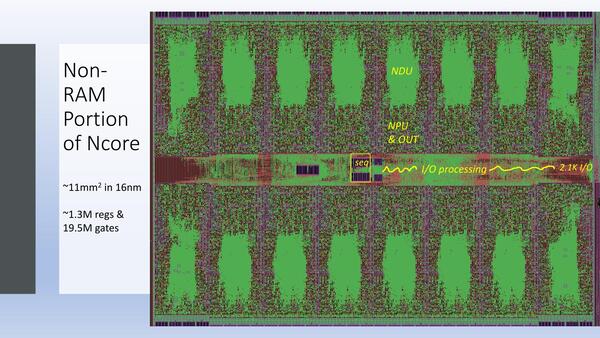

下の画像がNcoreのうちでロジック部のアップである。この部分だけで11mm2というのは、性能を考えるとかなり小さい方である。

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ