AI推論に不向きというx86の弱点を補うため

AI向けコプロセッサーを内蔵

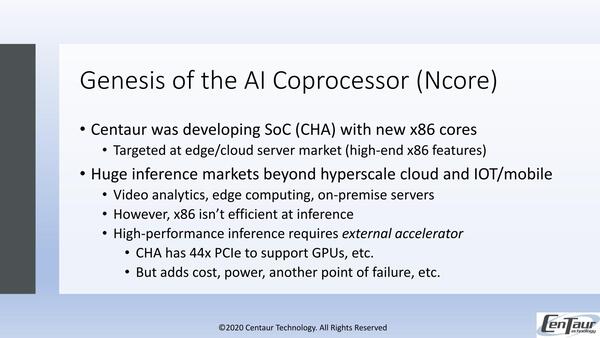

CHA+Ncoreの開発動機は下の画像の通り。もともとのCHAは、ZhaoxinがKX-6000シリーズとして提供しているものの後継を目指したSoCだったようで、ターゲットはサーバー市場である。

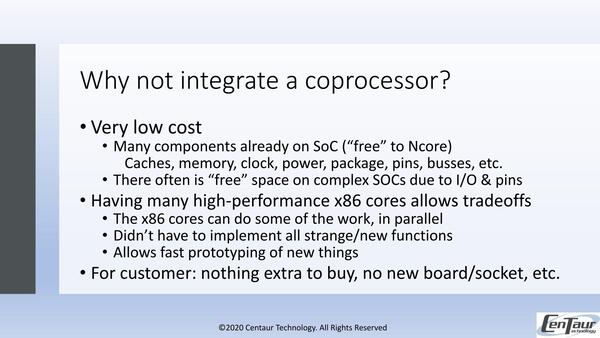

CHA+Ncoreの開発動機。CHAそのものは汎用で特にAIに向けたものではなく、例えばEdge Compute Serverを構築したければ、44レーンのPCI ExpressにそれこそNVIDIAのTeslaを4枚装着して、あとは10GbEカードなどをやはりPCI Expressでつなぐといった形を想定していた模様

といってもCentaurの場合は企業向けというよりも、エッジサーバーやクラウド向けで、どちらもそれほどの高い性能は必要ない。ここに向けて8コアのSoC構成だったのがオリジナルのCHAである。ただx86そのものはそもそもAIの推論に向いてないし、もっと言えば学習にも向いていない。

ではどうするか、というのは各社各様である。AMDは「推論も学習もGPUでやった方が効率が良い」というスタンスで、今のところCPU側にそれを取り込む計画はない(と言いつつも、トレンドにあわせて少しづつサポートするデータ型を増やすといった対応はしているが)。

逆に積極的なのがインテルで、AVX512のニューラルネットワーク拡張(AVX512VNNI)やCooper LakeでのBfloat16のサポートなど、本来AI処理に不向きなx86を力業で向く構造にしてしまっている。

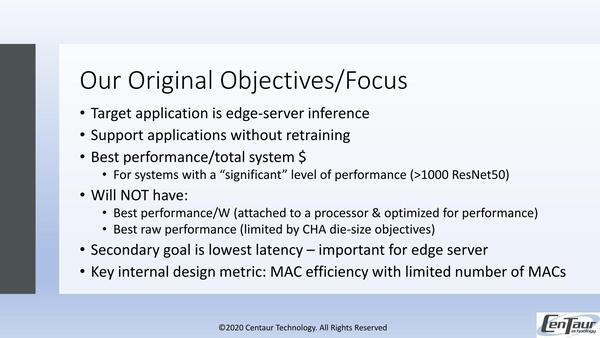

これに対してCentaurは、素直にAI向けコプロセッサーを内蔵するという方法を選択した。

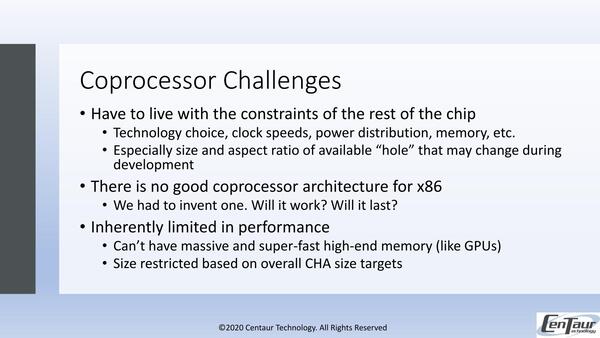

もちろんこの方式でもいろいろチャレンジはあるわけで、その結果としてCentaurはコストあたり最大の性能を第一目標、低いレイテンシーを第二目標に定めた。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 - この連載の一覧へ