携帯電話やモバイル端末に

効果的なMCP

基板に複数のダイを載せて全体を1つのパッケージにしてしまうこのMCPという方式は、下記のような比較的良好な特徴が得られる。

- SoCにしにくい、複数のプロセスで製造されたダイをまとめて実装できる(例えばプロセッサーは28nmなどで、フラッシュメモリーは90nmで、DACなどのアナログ回路は130nmでそれぞれ製造し、最終的にこれを1つにまとめられる)。

構成の変更が容易。SoCは半導体製造の前工程と呼ばれる部分で全部製造する必要がある。ところがMCPの場合は、後工程と呼ばれる部分で組み合わせることになるので、構成変更がしやすい。例えば、ほとんど同じ製品ながら搭載メモリー量を256MB/512MB/1GBの3種類でラインナップさせることが容易に行なえる。

SoCに比べるとやや大きくはなるが、それでも別々のチップを組み合わせるよりもずっと実装面積および体積が小さくなる。

SoCに比べるとやや消費電力が増え、距離も数mmほど長くなるが、それでも基板上で複数のチップを直接繋げるケースよりも信号電圧を下げられるうえ、配線距離も短くなる。

こうしたこともあって、携帯電話向けのSoCは、ほとんどがMCPの構成を取っている。携帯電話向けのSoCは、大半の部品は集積しているものの、さすがにDRAMまでは集積しきれないからだ。そこでDRAMをSiPの形で搭載しているわけだ。つまり、SoCとMCPは必ずしも相反するものではなく、補完しあう関係にあると考えてもらってよい。

MCPの実装方法

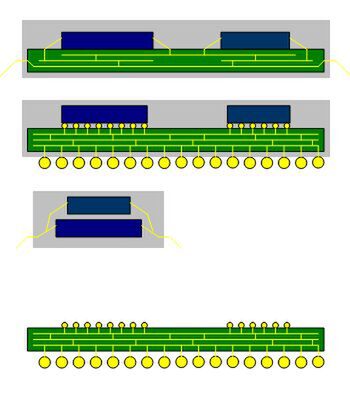

ちなみにMCPの場合は、様々な実装方法がすでに利用されている。上図の一番上側が、最初に考えられた方法であるが、中段のようにリード線ではなくボールを介して繋ぐ方法、下段のように複数のチップを積み重ねてリード線を繋ぐ方法、あるいはさらにチップの間にインターポーザーを挟む方法などもある。

積み重ね方式は、PC向けのチップでは発熱が多すぎて放熱に支障をきたすのでほとんど使われないが、携帯電話向けのチップは発熱が少ないので、積層してもそれほど支障ないということで広く使われている。

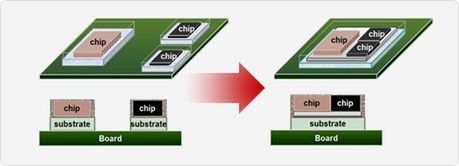

これをさらに進化させたのが、2.5Dや3D実装と呼ばれるものだ。2.5Dは図の中段の構成に近いが、異なるのは通常の基板ではなくシリコンインターポーザーと呼ばれるものを使ってチップ間を配線することだ。

通常の基板ベースでは、チップ間の配線は大雑把に見積もって数百本が限界であるが、シリコンインターポーザーではこれを1桁増やせる。また配線抵抗を減らせるため、省電力あるいは高速化にも貢献する。

最初にこれを商用製品に投入したのはXilinxのFPGAであるが、今年に入ってTSMCがCoWoS(Chip-On-Wafer-On-Substrate)という名称で広く利用できるサービスを開始している。

CoWoS(Chip-On-Wafer-On-Substrate)。TSMCのウェブサイトより抜粋

CoWoSの仕組み。TSMCのウェブサイトより抜粋

この先にあるのが3D実装である。これはTSV(Through Silicon Via:Si貫通電極)と呼ばれるものをダイに設け、物理的に垂直にダイを積層、配線するという仕組みである。ただこのTSV、研究は色々進んでいるものの、コストを削減するうまい手立てが見つからないということで、未だに実用化に至っていない。

この連載の記事

-

第770回

PC

キーボードとマウスをつなぐDINおよびPS/2コネクター 消え去ったI/F史 -

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ - この連載の一覧へ