数回にわたってSoCの根本的なことを説明していくSoC技術論。今回はさらに根源に戻って、LSIを作る手順をおさらいしよう。

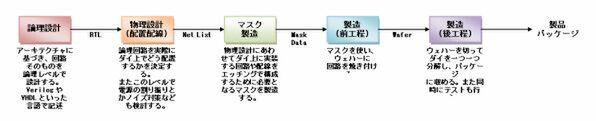

IC製造の流れ

まずは論理設計

上図はものすごくラフにLSIの作り方を説明したものである。これはCPUのような単機能(というのも変だが)だろうが、SoCだろうが変わらない。一番最初に来るのが論理設計である。

例えばCPUであれば、「どんなアーキテクチャーにするか」「どんなパイプライン構成にするか」から始まって、具体的なパイプラインステージの内部構成や、それを取り巻く回路をすべて設計するのがこのステージである。

論理設計は極端に設計期間にばらつきがある。例えばまったく新しいCPUを作り出した場合、CPUならばPentium、Pentium Pro、Atom、Pentium 4、K7、Bulldozer、Bobcatなどは数年のオーダーで期間がかかる。

SandyBridgeからIvyBridgeへ、BulldozerからPiledriverといった小変更では、変更箇所のみの修正なのでそれほど期間はかからない。もっと少ないのは、若干の修正、例えばPentiumのFDIVバグの修正やPhenomのTLBエラッターの修正などであれば、これは数日~1週間のオーダーである。

ちなみにSoCの場合は、単にCPUコアそのものだけではなく、メモリーコントローラー、内部バス、GPU、周辺回路と、さらに設計を行なうべき回路が増える分、大雑把にいってより手間がかかる。

CPUだけでも通常数百人の設計者が同時に設計を行なうのが一般的だが、SoCになるとこれが千人単位になることも、ままある。これは回路の複雑さに応じて規模が大きくなるというだけの違いである。

配線を決める物理設計

論理設計が一段落すると、次は物理設計になる。論理設計と物理設計の違いは、なにをどう配線するかを物理的に決めましょうということである。などと書いても、うまく連想できない方も多いだろう。そこで実例で解説しよう。

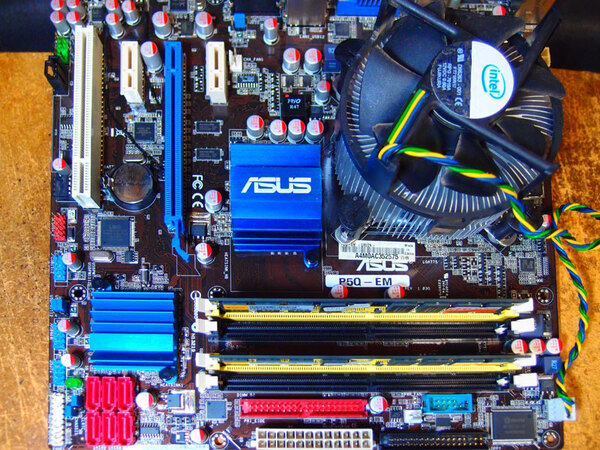

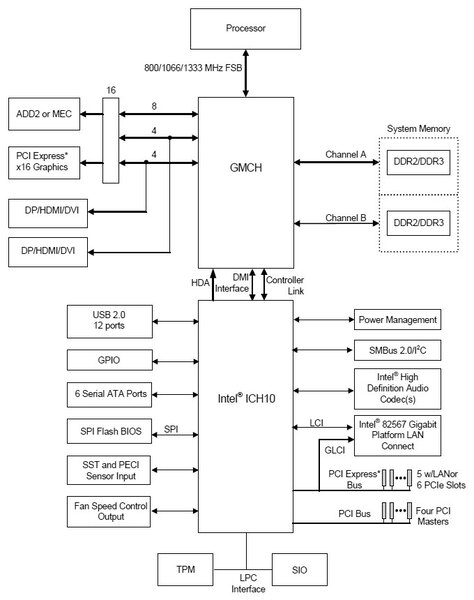

上の写真は、ASUSの「P5Q-EM」というLGA 775世代のマザーボードだ。これを例に取ったのはたまたま机の脇にすぐあったから、という以上の理由はない。さて、これはG45+ICH10という構成であり、基本的なブロック図は下の写真のようになる。

ここで規定しているのは、たとえばG45(GMCH)から2本のDIMMの配線が出てくるので、これを直接DIMMソケットに接続しましょうというもので、あとは「配線が等長になるように」という注意書きがあるだけだ。厳密にはもう少し電気的にさまざなな決め事があるのだが、それは割愛する。

実際にマザーボードとして構成するには、恐ろしくさまざまなパラメーターが関係してくる。まずチップセットとCPUソケットをどう配置するかだ。これはCPUクーラーの大きさなども関係してくる。離した方が大きなCPUクーラーを付けやすく、商品性が高まる一方で、距離が長くなると遅延が大きくなるし、そもそもMicro ATXのサイズに収まりにくくなる。

DIMMソケットにしても2本(1本/チャンネル)なのか4本(2本/チャンネル)なのか、あるいは拡張スロットをどうするのか、こうした大枠の設計にあわせて、実際の配線は非常に困難になる。

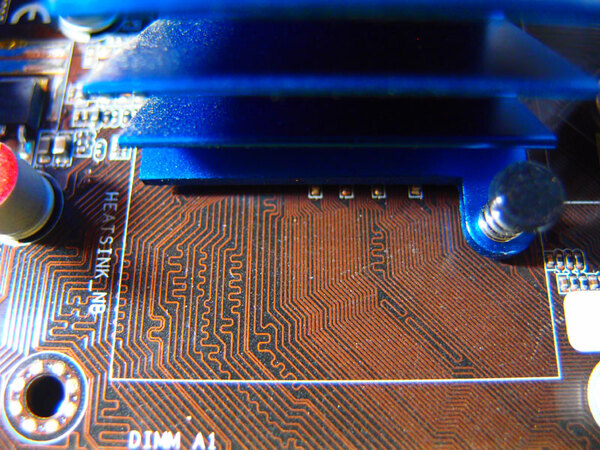

上の写真はGMCHとDIMMスロットの間のものだが、これにしても配線の基準長を自分で定めた上で、その基準長に合わせての迂回配線を随時行なう必要がある。この配線は、例えばGMCHの位置が5mmずれただけで全然違う形になってしまうわけで、最適値なるものを見つけるのは非常に面倒である。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ