SoCの利点はコストと消費電力

そして配線の短絡化

SoCはなぜ利用されるのだろうか。それは以下の3つが答えとなる。

- 低コスト化(省パッケージ化、部品点数削減、実装コスト削減)

- 低消費電力化

- 高速化

この中で一番大きいのは低コスト化である。特にスマートフォンなどの民生機器向けの場合、よほどのことがない限りは「コストダウン」が要求のかなり上の方に来る。そのため、周辺回路まで統合してワンチップ化することで、トータルでの部品原価や実装面積を減らすのはコストダウンに対する効果的な対策である。

加えて、特に携帯向けの場合は絶対的なサイズを抑える必要があるため、複数のチップに分かれていたシステムを1チップ化することは、それだけで大きなメリットになる。

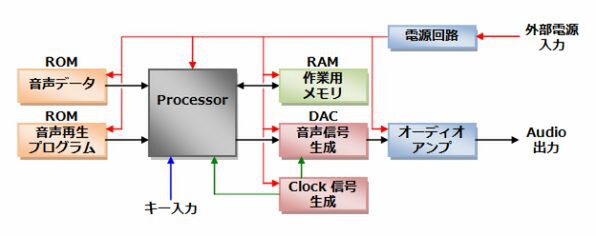

次の低消費電力化と高速化は、表裏一体である。まず最初に断っておくと、SoCにしたからCPUが高速になるなんてことはまったくない。CPUなりGPUという高速なコンポーネント単体は、SoCにしようがしまいが性能に差はない。ではどこに違いがあるかというと、コンポーネント間の接続である。

図に戻ると、もしもRAMが外付けになっている場合、それをSRAMで構成したとしてもインターフェースそのものは3.3Vや1.8Vの電圧で、しかも結構な速度で動作させる必要があるため、インターフェースに費やす消費電力が馬鹿にならない。また、実装の関係で、CPUとRAMの間は数cm~最大で10cmくらいの配線を引っ張りまわす必要がある。

ところがSoCにすると、信号電圧はSoC内部で利用する1V前後で、距離は長くても数mm、現実としては数十~数百μmである。つまり、コンポーネント同士の接続を、より高速かつ低消費電力で実現できるのがSoCのメリットである。

Systemをワンパッケージ化する技術は

SoCだけではない

これまでSoCのメリットを取り上げてきたが、なんでもかんでもSoCにしてしまうのは商品の柔軟性を欠くことになる。

SoCの開発にはコストと時間が多くかかるので、細かく仕様を変えてあれこれ作るのは非現実的である。SoCを作る場合、なるべく仕様を変えずに大量に量産しないと採算が合わない。

こうしたことを受けて、System全体をワンパッケージにする技法は昔から開発されてきた。その代表例がSiP、あるいはMCMと呼ばれるものである。

SiPはSilicon in Packageの、MCPはMulti-Chip Packageの略だが、どちらもほぼ同じものを指しているので、以下はMCPで用語を統一する。

MCPの代表例といえば、PCの世界では「Pentium Pro」だろう。下図のように、基板(インターポーザー)上に複数のダイを載せ、間を繋いだうえで、全体を1つのパッケージにしてしまうやり方だ。

エルピーダのメモリー製品に使われたMCPの技術紹介。一番下はベースにフリップチップで接合して、ほかのチップはワイヤボンディングで結ぶ、あるいは全部ワイヤボンディングで配線する

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ