ハイパースケールデータセンターを実現する次世代のサーバー&ストレージ 第2回

メニーコアプロセッサーで「手のひらスパコン」を実現!

ビッグデータを変える!Xeon Phi搭載サーバーの可能性

2013年09月03日 09時20分更新

単にXeon Phiを載せただけではない「HR120a-1」

こうしたXeon Phiへの高い期待は、搭載サーバーの製品化をいち早く進めたNECも同じ。Express5800/HR120a-1の製品を企画したNEC ソリューションプラットフォーム統括本部 商品マーケティンググループ マネージャの多賀 篤氏は、今後データ爆発社会の到来するにあたって、いわゆる利用されていないデータの活用が大きな課題になってくると指摘する。

NEC ソリューションプラットフォーム統括本部 商品マーケティンググループ マネージャ 多賀 篤氏

多賀氏は、「従来は必要なデータのみを選別し、処理しきれないデータを捨てていました。『データサイズが膨大すぎ処理ができない』『処理ができても時間がかかりすぎる』『今までよりも処理が複雑』。こうしたビッグデータ処理の課題を解決し、新しい付加価値を生み出せるサーバーを世に送り出したいと考えました」と、Express5800/HR120a-1の開発背景について語る。これを実現すべく、Xeon Phi登場の約2年前からインテルと緊密な情報交換や連携を進め、いの一番にメニーコアサーバーの開発・製品化にこぎ着けたのだ。

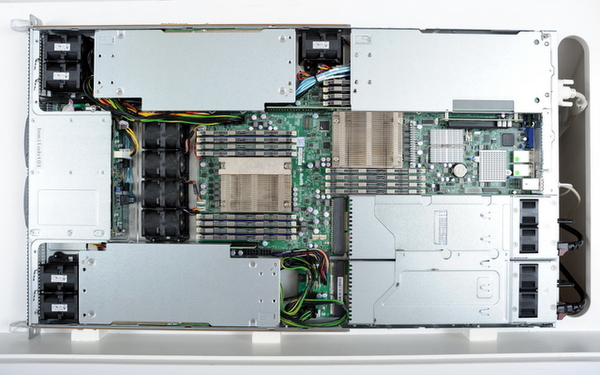

1U筐体のラックマウントサーバーであるExpress5800/HR120a-1は、Xeonプロセッサー E5製品ファミリー2基を搭載。DDR3-1600のECC付きメモリを最大512GBを搭載できるほか、高速な10GBASE-Tのネットワークインターフェイスを標準で2つ搭載(2CPU時のみサポート)。ストレージは2.5インチのSAS/SATA HDD 4台を搭載するほか、Xeon Phi専用のPCIeスロットのほか、RAID用のPCIeスロットも用意した。全体として、Xeon Phiの性能を活かす高い性能のハードウェアとなっていることがわかる。

Express5800/HR120a-1で重要なのは、単にXeon Phiを載せただけではないという点だ。

実機を見てみると、決してコンパクトとは言い難いXeon Phiのユニットを1Uの筐体に収めていることに驚く。そして、実機を開けてみると、その高い実装密度に感心する。

メインCPUであるXeonプロセッサーの横にXeon Phiユニットがそれぞれ2基。ストレージベイや16ものメモリスロットのほか、冗長化電源もきちんと2つ内蔵しているため、隙間らしい隙間は筐体前面の中央部分しかない。このわずかなスペースにメインCPUの冷却ファンを配し、前面吸気・背面排気のエアフローを作り出しているわけだ。多賀氏は、開発の苦労について「外部インターフェイスを搭載するスペースを確保しつつ、CPUとインターフェイスの物理的な距離も最短にするように配線しました。なおかつ、メインプロセッサーやXeon Phiの冷却にも配慮しなければならず、苦労しました」と語る。

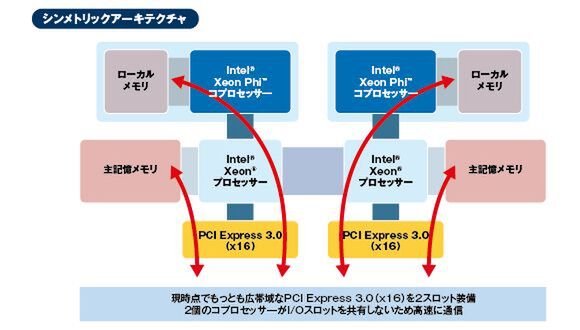

また、Express5800/HR120a-1では、I/Oを最適化し、CPUとコプロセッサーをバランスよく配置することで、Xeon Phiの性能を最大限に引き出しているのも大きな特徴だ。具体的には、PCIe3 x16スロットを用いた高速なI/0を、2つのXeonプロセッサーのそれぞれに割り当ている。「ビッグデータの処理を行なうためには、外部とのインターフェイスが重要になります。せっかくXeon Phiで大量の計算をしても、データの入出力が追いつかないと、トータルでパワーを発揮できません。そのため、HR120a-1は非常に幅広いI/O帯域を確保しています」(多賀氏)。この「シンメトリックアーキテクチャ」により、I/Oのレイテンシを短縮し、バンド幅も確保しているのだ。

I/Oのレイテンシを短縮し、バンド幅を確保したシンメトリックアーキテクチャ

(次ページ、Xeon Phiのフル活用でリアルタイムな超解像処理を実現)

この連載の記事

-

第3回

サーバー・ストレージ

性能と安定性でさくらが選んだNECの「iStorage M300」 -

第1回

サーバー・ストレージ

HPCとビッグデータは融合!ハイパースケールなインフラへ -

サーバー・ストレージ

ハイパースケールデータセンターを実現する次世代のサーバー&ストレージ - この連載の一覧へ