インテルは27日、コード名「Nehalem-EX」と呼ばれる開発中のマルチプロセッサー(MP)サーバー向けCPUの概要を公開した。1つのCPUダイ上に8個のCPUコアを集積した、x86系CPU初のオクタ(8)コアCPUとなる。

今回公開された情報は正式な製品発表ではなく、あくまで概要である。ブランド名は従来どおり「Xeon」を継承すると思われるが、製品名やラインナップ、クロック周波数、価格などは発表されていない。

8コア内蔵で16スレッド同時実行

共有3次キャッシュは24MB

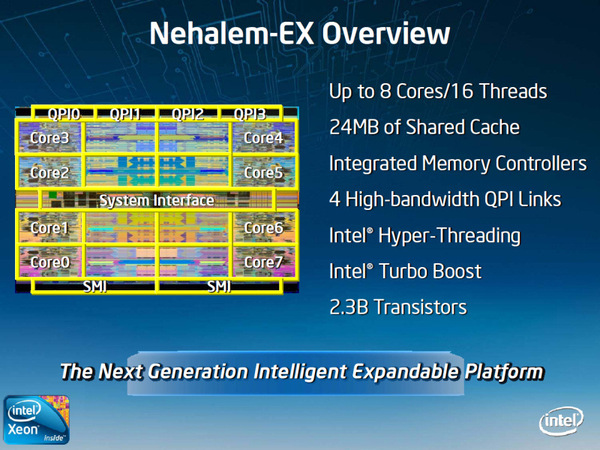

Nehalem-EXは、デスクトップパソコン向けのハイエンドクアッドコアCPU「Core i7」や、デュアルプロセッサーサーバー向けCPU「Xeon 5500番台」と同じく、Nehalemアーキテクチャーを元にしたCPUである。Nehalemの特徴である、3層構造のキャッシュメモリー、メモリーコントローラーの内蔵、インターコネクトバス「QPI」の採用、ハイパースレッディング・テクノロジー(HT)やターボ・ブースト・テクノロジー、バーチャライゼーション・テクノロジー(VT)への対応といった特徴は、そのまま継承している。

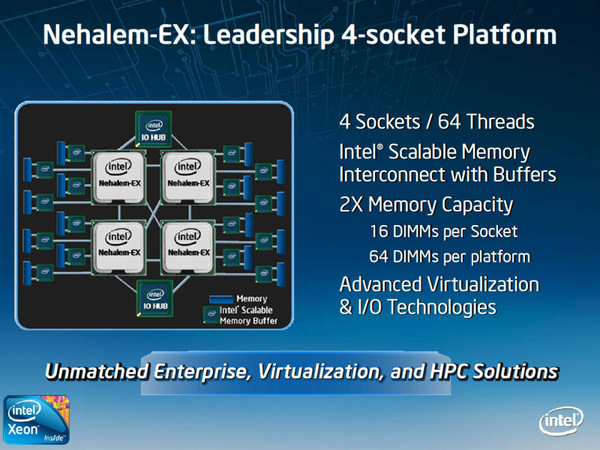

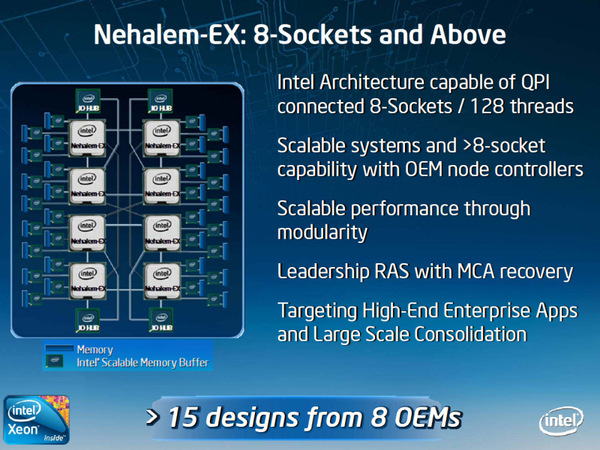

Nehalem-EXとXeon 5500番台の最大の違いは、ひとつの半導体ダイ上に8個のCPUコアを集積している点にある。8コアに加えてHT対応により、同時に16スレッド分のプログラムを実行可能となっている。また、CPUとチップセット、あるいはCPU同士を結ぶQPIを4本備える。これにより、4ソケットのMPシステムを構築する際に、4個のCPUパッケージそれぞれを直接QPIで接続でき、パフォーマンスを向上させられる。

また、Xeon 5500番台やCore i7が3次キャッシュを8MB内蔵するのに対して、Nehalem-EXは3倍もの24MBの3次キャッシュを内蔵する。製造プロセスは45nmプロセスで、トランジスター数は約23億個にもなる(Core i7は約7億3100万個以上)。

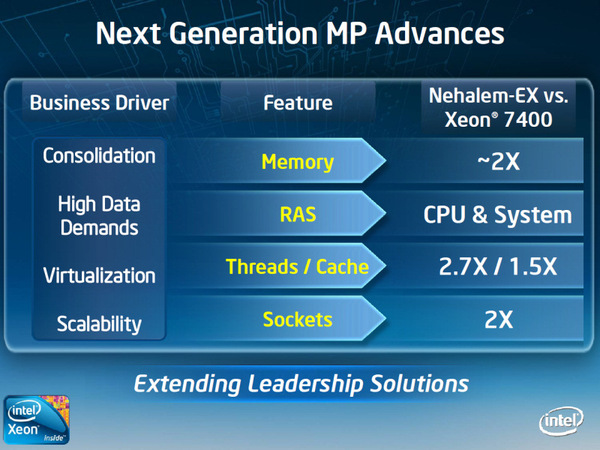

対応メモリーについては、Xeon 5500番台と同じくレジスタードまたはアンレジスタードのDDR3メモリーに対応するとのみ伝えられている。CPUとメモリーの間にバッファを設けることで、1ソケット辺り16枚のDIMM、4ソケットシステムならば最大64枚のDIMMを装着可能としている(Xeon 5500番台は9枚)

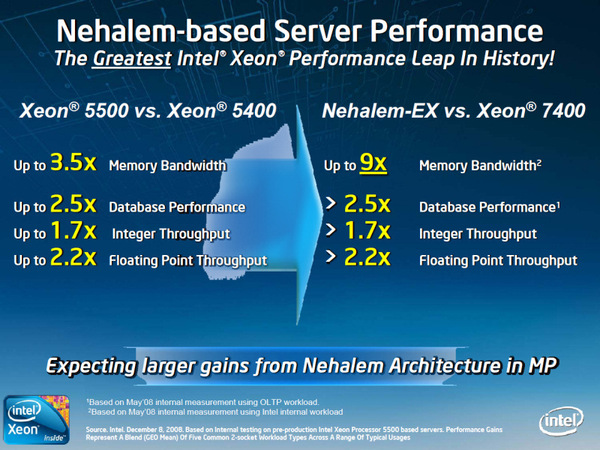

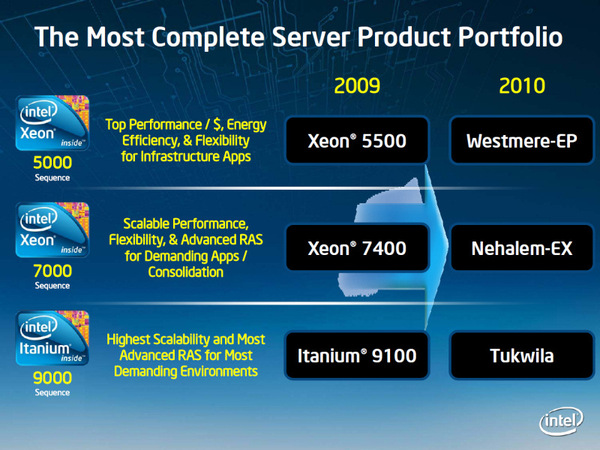

Nehalemアーキテクチャーと8コアによる性能向上は非常に大きい。インテルでは既存のMPサーバー向けCPU「Xeon 7400番台」に対して、9倍のメモリーバンド幅で整数演算性能は1.7倍、浮動小数点演算性能は2.2倍、データベースのパフォーマンスでは2.5倍の性能向上を実現できるとしている。

このNehalem-EXを搭載するシステムは、2009年第2四半期にはサーバーメーカー各社から出荷されるとのことだ。

この連載の記事

-

第20回

デジタル

レノボ・ジャパン、Xeon 5500番台対応のタワー型サーバ -

第19回

デジタル

レノボ、リモート管理に優れた中小向けサーバ第2弾 -

第18回

サーバー・ストレージ

富士通、2008 R2バンドルサーバで省エネを推進 -

第18回

サーバー・ストレージ

日本IBM、コストパフォーマンスと拡張性に優れたx86サーバ -

第18回

サーバー・ストレージ

日本IBM、Xeon 5500対応のブレードサーバ管理ソフト -

第17回

サーバー・ストレージ

HPCシステムズ、ダブルGPGPU対応のXeon 5500サーバ -

第16回

ビジネス

Xeon W5580を2基搭載、最高峰WSの実力を試す -

第15回

サーバー・ストレージ

日本IBM、オフィス向けのXeon 5500番台搭載サーバ -

第14回

デジタル

仮想化導入を短期化するデルの新製品とサービス -

第13回

サーバー・ストレージ

日本HP、クラウド向けサーバの新ブランド投入 -

第12回

サーバー・ストレージ

東芝、Windows Storage対応のXeon 5500サーバ - この連載の一覧へ