32コア以下の製品は3次キャッシュの容量が

Sapphire Rapidsと変わらない

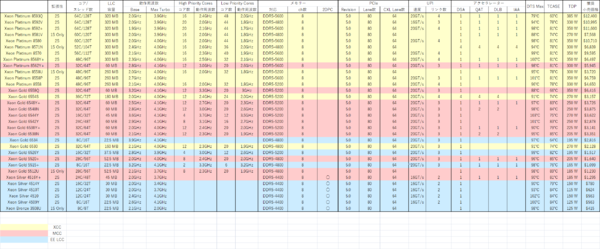

ではMCCは? というと、XCCのタイルをそのまま使うことはできない。というのはメモリーコントローラーとUPI/PCIeレーンの数が足りないからだ。SKU一覧では細かすぎるうえにいくつか落ちている項目があるので、Intel ArkからEmerald Rapidsのスペックを落としてまとめたのが表である。

全SKUともにPCIeが80レーン、DDR5も8ch搭載されている。周辺回路周りで言えば、XCCとMCCの違いは以下になる。

- UPIが最大3ch(3×16レーン)に(XCCは最大4ch)

- アクセラレーター(DSA/QAT/DLB/IAA)が各1個(XCCはすべて最大4つづつ)

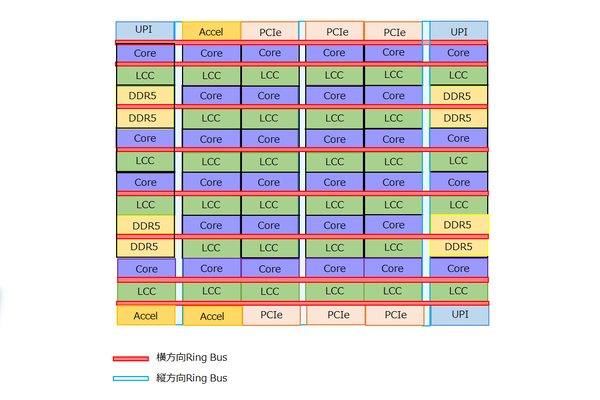

したがって、これをまともに構成した場合には、現在の7×5のブロックではどう考えても足らず、8×5ないし6×6ブロックになる。現実的に可能性が高いのは6×6ブロックで、構成としては下図のようになるだろう。

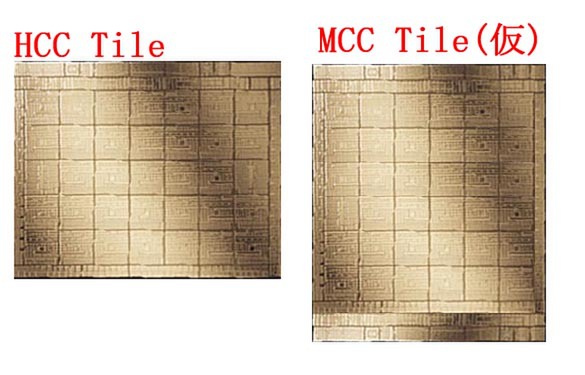

もしこれをXCCと「まったく同じ構成で」実現したとするとどうなるか? というと、XCCの7×6ブロック分の面積が28.2×20.5mmで、これを6×6ブロックに組み替えると24.1×24.5mmほど。さらにブロックの上下にアクセラレーターやPCIe/UPIブロックが配され、またブロックの横にはPHYのエリアが付くので、下の画像のような構成になるはずだ。

この場合最終的にタイルの寸法は26.8×31.2mmほどになり、面積は836.2mm2ほど。Reticle Limit(ダイサイズの限界)に挑戦というか、ややブッちぎっていないか? という寸法になる計算だ。いくらなんでもこれはおかしい。

実は上の画像の構成は、それぞれのコア+LCCがXCCとMCCで同じという前提で話をしている。ここでもう一度表を見て欲しいのだが、XCC、つまり黄色のものはLLC(Last Level Cache)容量がコア数×5MBになっている。ところがMCC、つまりピンクであるが、こちらは以下の4種類が存在する。

| MCCの種類 | ||||||

|---|---|---|---|---|---|---|

| コア数 | LLC容量 | |||||

| 32コア | 60MB | |||||

| 28コア | 52.5MB | |||||

| 24コア | 60MB | |||||

| 24コア | 45MB | |||||

このうち24コアで60MBなのはXeon Gold 6542Yのみで、他はLLC容量がコアあたり1.875MBとSapphire Rapidsと変わらない数字になっているのがわかる。

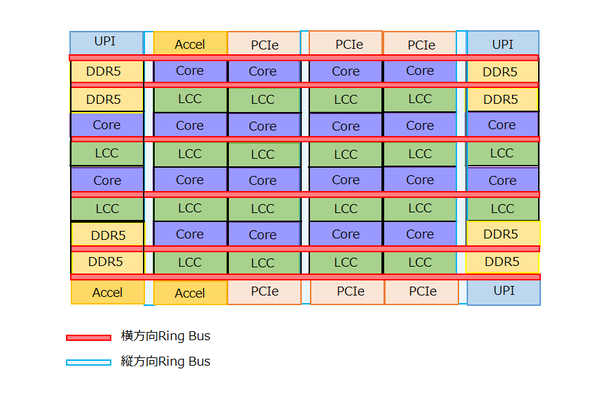

これはEE LCCも同じであり、32コア以下の製品は3次キャッシュ容量を据え置きにすることで個々のブロックの面積を減らしており、結果としてタイルの面積(上の画像で言えば高さ方向)を減らせると思われる。どの程度か? というのはもう少し細かい写真が出てこないとなんとも言えないのだが、3次キャッシュの面積が6割強減っているのはそれなりにインパクトがある。

例えばブロックの高さがこれで1割減ったとすれば753.1mm2、2割なら670.0mm2ほどになる計算である。3割までは減らないと思うので、実際は700mm2弱くらいではないかと思うのだが、そこまで減ればXCCのタイルより明らかに面積が減るので、それだけ歩留まりが上がり、原価も下がりそうだ。

ちなみにXeon Gold 6542YだけLLCが60MBなのは、コアは24コアのみ有効にしつつ、LLCは32コア分すべてを有効にしているのだろう。

EE LCCもコア数が20に減った以外はMCCと同じなので、下図のような構成だろう。正確なダイサイズは不明だが、仮にLLC 5MBだったとしても617.3mm2ほどなので、実際には500mm2台あたりで収まるものと考えられる。

この連載の記事

-

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 - この連載の一覧へ