Jim Keller氏お得意のRISC-Vで

CPUだけでなくチップレットの提供を目論む

ここからはRISC-Vコアの話に移りたい。先に説明したようにTenstorrent自身はRISC-Vコアを当初から扱っていたが、少なくともそのRISC-Vコアそのものでビジネスするつもりはなかったようだ。

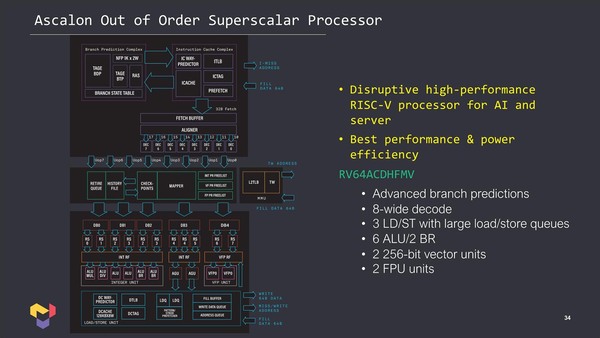

これが変わったのはやはりKeller氏の参加からだろう。まず最初にAscalonと呼ばれる8命令デコード/11命令発行のスーパースカラー/アウトオブオーダーのRISC-Vコアを設計をしている。

Ascalonの概要。連載706回で示したスライドと同じものだが、以前のスライドはディテールが潰れていたが、今回はだいぶクリアなものが示された

予想外だったのは、Tenstorrent(というよりKeller氏)はまずこのハイエンドコア(D6)を完成させ、次にこれのサブセットとして2/3/4/6命令デコードの派生型(D2~D5)を作ったという話だ。

普通は逆なのだろうが、すでにAMDやインテル、Teslaなどでこうした大規模なスーパースカラー/アウトオブオーダーのコアを作り慣れていたからこその技である。

このAscalongコアをまとめたクラスターや、それを組み合わせたチップレットという話はすでに報じたとおりだが、Tenstorrentは単にCPU IPを提供するのみならずチップレットの提供というビジネスも目論んでいる。

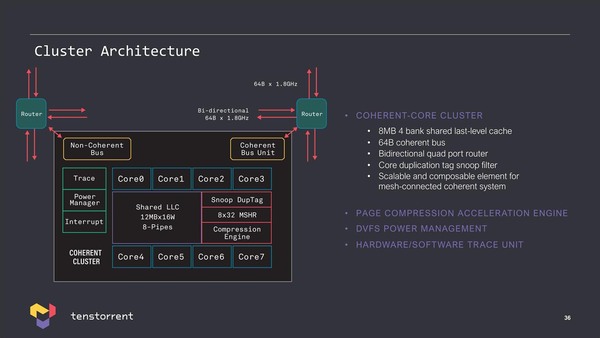

Ascalongコアをまとめたクラスター。以前のスライドと似ているのに、説明では8MB 4Bank LLCとなっているのに図では12MB×16WのLLCと、全然数字が合っていないように見えるのはどうしたものか

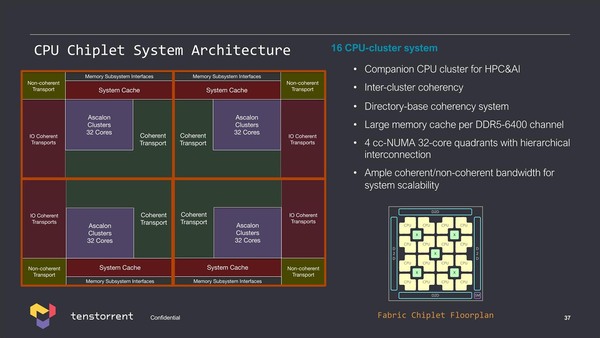

CPUチップレット。これも以前のスライドと似ているが、左は32コア(つまり2つ上の画像にある構成×4)が1つのCC NUMAノードを構成する128コアの巨大なシステム、右は16コアの小規模なチップレットのフロアプランと思われる

要するにビジネスとしては以下のことを考えているわけだ。

- CPU(RISC-V/AI) IPの提供

- CPU IPを使ったASICの設計支援

- CPU チップレットの提供

- チップレットを利用した独自チップの設計支援

実際、こうしたリソースを利用した商談は水面下で進んでいるが、特に後述する自動車向けではIPだけがほしいというところからチップレットの設計支援をしてほしいというところまで、さまざまなニーズが寄せられているそうだ。

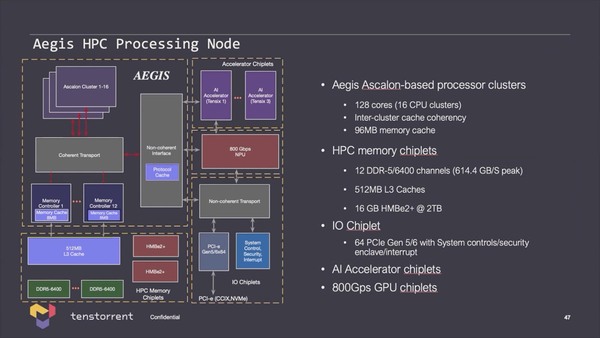

Tenstorrent自身、こうしたチップレットを今後は積極的に採用していくつもりらしい。Aegisと名付けられたHPC向けの設計では128コアのAscalonにAI アクセラレーターと周辺チップからなる5つのチップレット構成であるが、さらに大規模なTunderbolt-XMというチップのアイディアも披露された。

HPC向けのAegis。3次キャッシュが512MBなのはわかるが、CPUクラスター側からのI/Fはメモリーコントローラー×12というのがよく理解できない。16クラスターなのだから、×16ならわかるのだが……

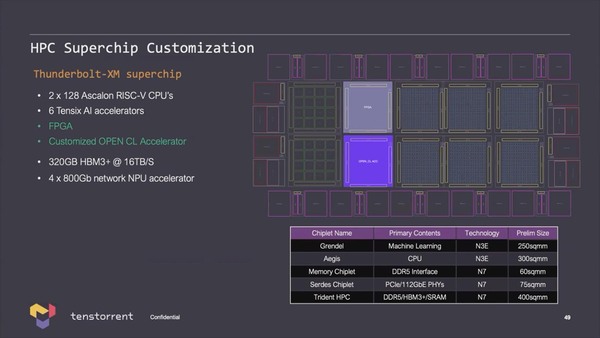

Aegisよりも大規模なTunderbolt-XM。ここではAIアクセラレーターがGrendelとして説明されているので、最初のページにある2枚目の画像に出てきたGrendelというのは、単にAIアクセラレーターチップレットの名前ではないか? というのが筆者の推定だ

上の画像では各チップレットの詳細も示されており、Aegis(128コアのAscalonのチップレット)はTSMC N3Eで300mm2、Grendelは同じくN3Eで250mm2とされる。その一方PHYやSRAMは全部N7での製造になっており、特にDDR5とHBM3 I/Fに加えてL3 SRAMまで搭載したTrident HPCは400mm2とかなりの寸法である。

図で見ると、このTrident HPCを10個搭載することになってるが、さすがにこれはいろいろ無茶ではないか? という気がする。実現可能性はともかくとして、技術的にはこうしたものまで提案できるというのがTenstorrentのRISC-V/チップレットビジネスというわけだ。

自動運転のアルゴリズム構築に使うスパコンを

日本の自動車会社に売り込むのが真の狙い

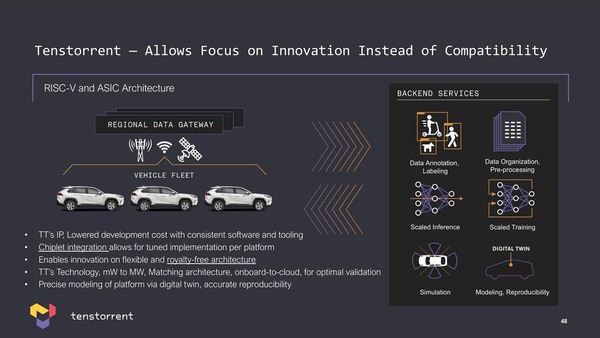

最後に自動車向けについて。日本支社が設立された目的は、当然日系の自動車会社を取り込みたいというニーズがあるからだろう。ただそのアプローチは、他社と明確に異なっている。

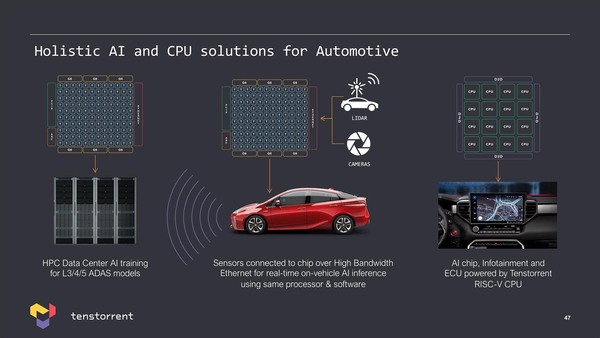

下の画像で示すTenstorrentの自動車市場を見ると、中央と右はよく見るが、左はかなり目新しい。

特にレベル3以上の自動運転を狙う場合、今後はコネクテッドカーの形でないと難しくなっていくと考えるのも無理はない。

連載709回でも説明したが、Teslaは自動運転のアルゴリズム構築のためにDojoスーパーコンピューターを自社で開発した。ただこれはTeslaだからできる技であって、普通の自動車メーカーは自社でAIスーパーコンピューターを構築できるような技術力はない。

ならそうしたニーズはないのか? というとそんなわけもなく、遠からず自車の運行データをネットワーク経由で吸い上げ、そのデータを元にアルゴリズムを迅速に改良していくというTeslaと同じような仕組みが求められるのは間違いない。

そうしたニーズが必要になる顧客、つまり自動車会社やティア1(自動車会社に直接部品などを納入する請負業者)に対して、Teslaでそうしたシステムを構築した責任者が(Dojoに負けないような)代替解決案を提供できます、というのはビジネス的に非常に説得力があるし、市場も期待できる。なるほど、真っ先に日本に海外支社を立ち上げたわけである。

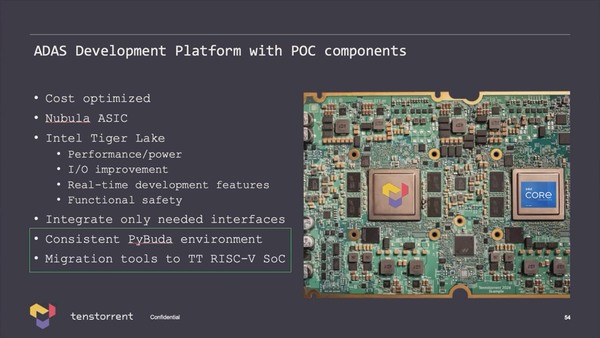

ちなみにすでにこうした目的に向けたPoC用の開発ボードが存在するそうだ。説明によれば、現時点ではホストとしてTiger Lakeが搭載されているが、これはPoC向けだからという話で、仮に製品化が進行するとしたらRISC-V CPUとNebulaを一体化したチップになるだろうとのことだった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ