今回はTachyumのProdigyを取り上げる。ちなみにTachyum自身はProdigyを“World's First Universal Processor”と称しているが、一般的にはAIプロセッサーと扱われており、筆者もこれに準じてAIプロセッサーとして紹介したい。

スロバキアとのつながりが強いTachyum社

創業者のDanilak博士はいろいろなプロセッサーを開発

Tachyumは2016年、Radoslav Danilak博士によって創業された。ちなみに本社そのものはサンタクララに存在するが、同社は限りなくスロバキアとのつながりが強い。Danilak博士自身、アメリカの市民権を持つが生まれはスロバキアであり、現在もスロバキア政府のInnovation Advisory Boardのメンバーを務めてもいる。

そもそもDanilak博士の経歴を見ると、スロバキアのDanSoft SroというVLIWプロセッサーを開発する会社を創業、CEO兼CTOを務める→Gizmo Technologyというx86互換プロセッサーの開発を目指していた会社のChief Architect→東芝でTX7901(MIPSベースのコアで、PS2で使われた)のSr.Staff Processor Architect→nishan systemという会社でネットワークプロセッサーのSr. Processor Architect →nVIDIAでnForce 4/nForce 4 Intel Eedition chipsetのSr Architect→SandForceの創業者兼CTO→ディスクコントローラーを作るSkyeraという会社を創業→同社の買収にともないWDでCTO→Tachyumを創業といった具合に、さまざまな企業を創業してはいろいろなプロセッサーを開発していたそうだ。

また、どうも連載568回で紹介したWave Computingで10GHz駆動のDPU向けプロセッサーエレメントの開発にも関係していたことがあったらしい。

PCIe Gen5とDDR5、HBM3まで搭載する超欲張りセット

VLIWというあたりにItaniumと同じ匂いを感じる

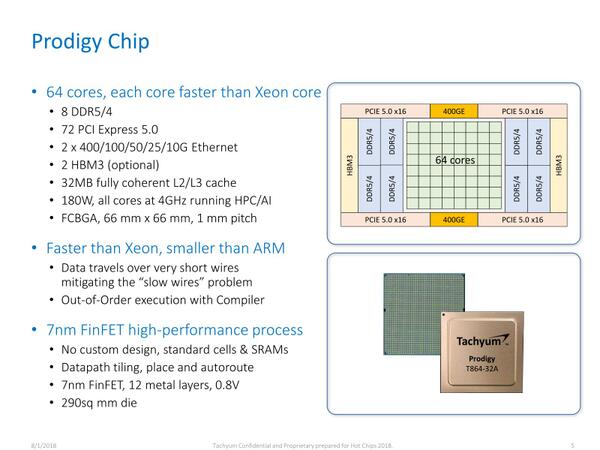

そんなTachyumであるが、2018年のHotChipsで、同社のProdigyチップの詳細を初めて公開した。ProdigyはいくつかのSKUがあるが、ハイエンドは64コア構成となっている。CPUコアと32MBキャッシュ、DDR4/5×8ch、400Gイーサネット、PCIe Gen5 x72と周辺回路も盛り盛りで、さらにオプションでHBM3まで搭載という、超欲張りセットである。

これをTSMCのN7で製造し、全コア4GHz駆動で消費電力がたったの180Wというのは、もう「僕の考えた最強(最狂?)CPU」という感じで、シミュレーションの数字なのか願望なのか外部からは判断できない。

なぜこれが実現できるか? と言えば、個々のコアが「Armコアより小さく、Xeonより高速に動作するから」であるが、その理由の1つが「Out-of-Order execution with Compiler」というあたりに、Itaniumと同じ匂いを感じてしまう。

ちなみに設計は一切カスタム設計はなく、TSMCのStandard CellとSRAMで構成され、配置配線もEDAによる自動配線で設計しており、それでダイサイズは290mm2というから、かなりコアそのものは小さいということになる。

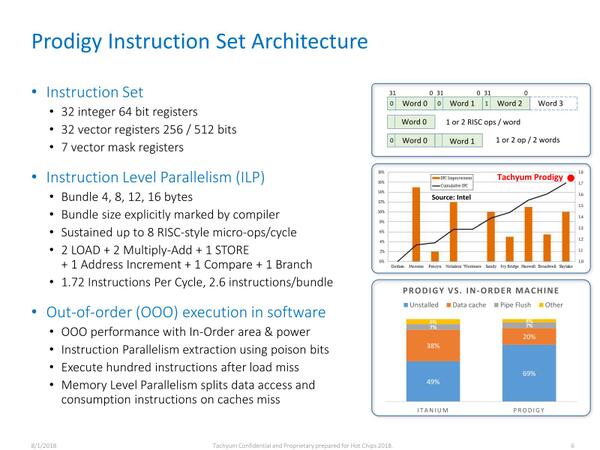

そのコアの命令セットが下の画像だ。最大4命令をバンドルできる、というあたりでVLIWであることは確定である。内部ではさらにこれをmicro-opに変換するようで、最大8 micro-opsのVLIWということになる。

中央のグラフは、左軸が縦棒(前世代からのIPC向上率)、右軸が折れ線(累積でのIPC向上率)で、Dothan世代が基準らしいが、ProdigyはSkylakeより少しマシ程度、ということになる。もっともアーキテクチャーが異なるので、この比較に意味があるのかは謎だ

もっとも命令そのもので言えば、演算はMAC×2で、あとはLoad/Store/Compare/Branchなどが占めていることを考えると、そんなに極端に演算処理に振っているわけでもない。Prodigyではこの1~4命令をまとめた物をBundleと称しているが、1命令がおよそ1.72 micro-op相当、1 Bundleが2.6 micro-op相当なので、VLIWといっても無理やりにIPCを引き上げている感じはしない。

このあたりはむしろ堅実な設計という気はするのだが、それをすべてぶち壊している感じがするのが“Out-of-order execution in software”である。コンパイラ屋さんが憤死しそうな話ではあるが、要するに

- VLIW方式なのでデコードが非常にシンプルであり、余分な動作が入らない

- 命令実行はハードウェア的にはIn-Orderなので、処理コストのかかるDispatcherやSchedulerが不要になる

In-Orderがゆえに通常問題になる、データ待ちによるPipeline Stallなどは、コンパイラの側で対応するので(←これがわりと無茶)、ハードウェア的に余分な機構を用意せずに高効率で実行できる。

ということで、Armに比べてもはるかに小さい回路サイズで実現が可能であり、回路サイズが小さいということは動作周波数を上げやすいということになる。とりあえずコンパイラ屋さんの苦悩を無視すれば、これは理解できる方針である。そのコンパイラがしばしば仇になることが多いのがVLIWの歴史でもあるのだが。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ