ロードマップでわかる!当世プロセッサー事情 第645回

ET-SoC-1の設計思想で納得、やっぱりEsperantoはDitzel氏の会社だった AIプロセッサーの昨今

2021年12月13日 12時00分更新

Esperanto Technologies, Inc.と、ここの開発したET-SoC-1の話は連載594回で一度紹介している。この時はまだ動作するシリコンが存在せず、それもあってかいろいろ中身が不明な部分も多かった。

ところがその後同社は動作シリコンやこれを利用した評価ボードの提供などを実際にスタートしており、今年11月にオンラインとオンサイトを併用する形で開催されたRISC-V Days Tokyo 2021 Autumnで、わりとディープな内部構造が公開されたので、このあたりのアップデートをお届けしよう。

合計1093コアもあるのに

消費電力はわずか20W以下

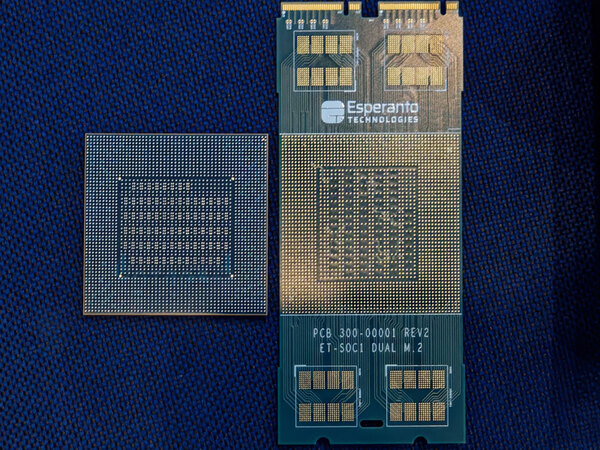

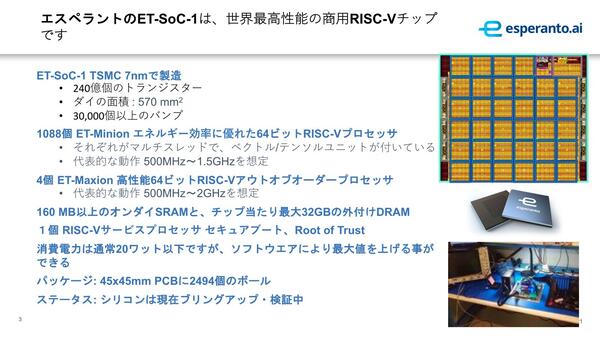

まずET-SoC-1の概略が下の画像だ。以前も説明したが、ET-SoC-1はET-MaxionとET-Minionという2種類のRISC-Vコアで構成される。

ET-Minionが1088個(32コア×34グループ)、I/Oやアプリケーション制御用のET-Maxionが4つ、それとセキュアブート可能なサービスプロセッサー(以前はこれがET-Minionベースと説明があったが、最終的にこれがどうなったかは不明)の、合計1093コアからなる、ちょっとしたお化けである。

ダイサイズも570mm2と、昨今のAI向けプロセッサーではむしろ控えめなのかもしれないが、一般的に言えばかなり大きい。ただそれより特筆すべきは、通常20W以下というあり得ない消費電力であろうか。

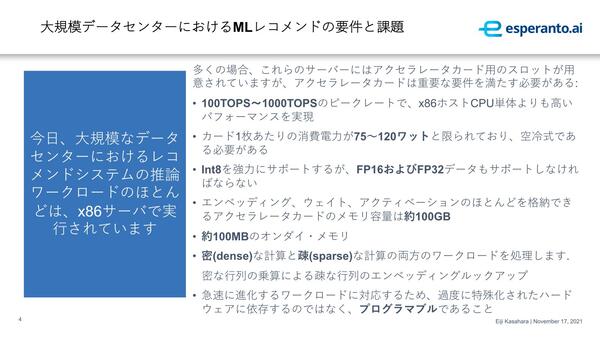

もちろん20W以下のチップの例はある。QualcommのCloud AI 100は、15W/25W/75Wの3種類のSKUがあるし、エッジ向けなら例えばAiOnIcのものは1.5Wや(パートナー製品でも)5Wなどなので、ずっと小さい。ただ1000コア以上のコアを集積して20Wというのは、例がない。この20Wというターゲットはどこから出てきたか? というのが下の画像だ。

拡張カードはPCIeベースだから仕様上は300W/枚までいけるが、現実問題として電源ユニットや冷却の関係を考えると、120W程度に収めたいというニーズがあり、これにあわせたものだとしている。

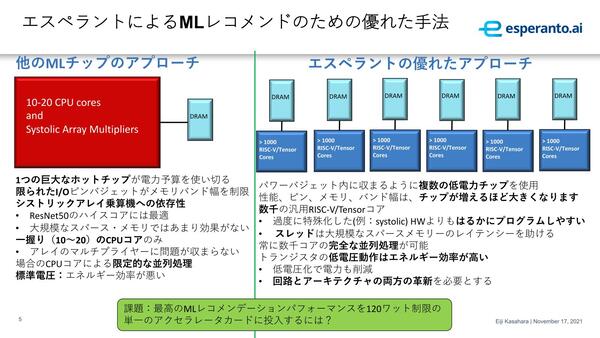

この120Wという枠をどう使うかという話で、Qualcommの場合ではCloud AI 100を1チップ/75Wに抑え、その分カードの数を増やすという方向に振ったが、Esperantoは20W駆動のチップを6つ搭載する方向に舵を切った。

このあたりはバランスをどうとるかという話でもあって、12Wのチップ×10ではメモリー帯域に対して性能が十分ではないだろうし、30W×4だと性能に対してメモリー帯域が足りなくなりそうな感じだ。20Wのチップ×6というのはEspelantoなりに一番バランスの取れた構成ということなのだろう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ