ロードマップでわかる!当世プロセッサー事情 第625回

脳の神経細胞を模したSNNに活路を見出すInnatera Nanosystems AIプロセッサーの昨今

2021年07月26日 12時00分更新

これまでたくさんのAIプロセッサーをご紹介してきたわけだが、ほとんどのものはCNN(Convolution Neural Network:畳み込みニューラルネットワーク)に対応したものである。CNNの理屈は連載561回で紹介したが、脳の構造をそのまま模式化するのではなく、勾配法を使ってシミュレーションするような形での実装になっている。

ただ連載561回で説明したように、そもそものニューロンとシナプスのモデルはあくまで神経パルスである。この神経パルスの構造を維持したままニューラルネットワークを構築できないか、ということでやはり研究と開発が進んでいるのがSNN(Spike Neural Network)である。

結論から言えば、今のところSNNがCNNを凌駕する点は1つだけで、推論精度が特に良くなったり、学習が高速化するようなことはない。逆に言えば、SNNにしたことでCNNから失われるものがあるかというと、原理的にはそれもほとんどなかったりする(現実には存在するが)。

ではそのメリットはなにか? というと消費電力である。実際の神経細胞の場合、伝達されるのはパルスであって、その数や頻度で次の「発火」が行なわれる。これを実際にプロセッサー側で模式化すると、値が1bitになる。その意味では1bitのCNN(BNN:Binary Neural Network)とかなり近いものになる。

昨今のCNNの問題点は、ある程度の精度を出すために2bit以上のデータを保持することが多く、消費電力は純粋にデータのサイズに比例することを考えると、SNNはCNNに比べて圧倒的に消費電力が少ないというのが大きなメリットとなる。

ではデメリットは? というと既存のCNN向けプロセッサーの上でSNNにしても、省電力にも高速にもならないことだ。例えば8bit型を扱えるプロセッサーの上でSNNを動かしても、単に7bit分の演算ユニットが遊ぶだけで、8倍高速になるわけではない。8bit×1を1bit×8に分割できるような機構を入れない限り、まったく高速化は望めない。

したがって1bit演算ができるプロセッサーを作らない限り、SNNのメリットは皆無ということになる。SNNというかBNNに関して言えば、XilinxやLatticeといったFPGAベンダーがBNNを実装したものをいくつかリリースしている(製品という意味ではなくIPとして提供しているという意味だ)。

Latticeで言えば、例えば2018年には同社のiCE40という非常に小型のFPGA上でBNNを稼働させ、顔認識を実行するデモが行なわれている。

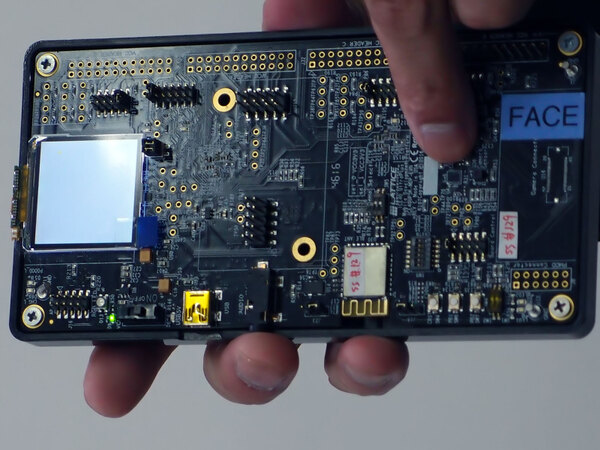

これはLattice社の日本オフィスでのデモの風景。これはiCE40の評価ボードで、指先の小さなICがiCE40本体だ。このデモでは、カメラ(これは指先の少し右にある黒っぽい立方体)で写した画像が人間の顔かどうかをBNNで判断、顔の場合はLED(指で隠れていて見えない)を光らせるというもの

利用したのはiCE40 UltraPlus(https://www.latticesemi.com/ja-JP/Products/FPGAandCPLD/iCE40UltraPlus)という2800ないし5280LUTを搭載する超小型FPGAで、BNNの実装に3K LUTほど占有する関係で大容量の5280LUT版が必要になる。こちらは単体だと1個600円程度の価格だが、普通(つまりもっと大口購入)だと500円を切る安価なFPGAである。

例えば自動販売機にこれを仕込んでおき、カメラでずっと監視して販売機の前に人が立った時だけ照明をオンにする、という使い方がこれで可能になる。目的が省電力なので、常時照明を点けている場合より消費電力が増えたら監視の意味がない。

昨今では、照明もLEDを使って省電力に配慮しているわけで、それよりもさらに消費電力を下げたい(ついでに言えば省電力のために高コストなAIプロセッサーは入れられない)というケースでは、BNNを使ってネットワーク規模を小さく抑えることで、省電力かつ低コストに実装が可能というわけだ。

これはあくまでBNNの話で、SNNそのものではない。BNNとSNNではそもそも理屈が異なるし、実装も異なる。BNN用のプロセッサーでSNNをそのまま動かせるわけでもない(逆もまたしかり)。ただBNN用のプロセッサーとSNN用のプロセッサーは、必要とされるハードウェア構成がかなり近いのは事実だ。実装は異なるとはいえ、SNNもBNNと似たような市場を志向している。

加えて言うと、CNNとSNNの違いの1つに時間軸がある。CNNの場合、例えば1枚の画像を取り込んで処理する際に、ネットワークのある層から次の層へのデータ転送は1回である。前の層で処理を行ない、その結果を1回送りだしたら、前の層は(次のデータが来るまで)お休みである。

これに対しSNNでは、例えばパルスが3回到達したら「発火」するという具合に、データの処理は一律には行なえない。言ってみればストリーム処理的な対応が必要になる。人間のシナプスの場合、一度「発火」すると、そのあと一定期間「発火しない」時間がある。こうした特性まで取り入れると、さらに時間軸方向で同期がとりにくい。

ただこれは、例えばセンサーデータを随時取り込んでいくといった用途にはむしろCNNより向いているという見方もでき、実際そういう方向での研究も進んでいる。これはニューロモーフィック・コンピューティングなどと呼ばれることもある。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ