米国時間の8月13日、インテルは突如としてArchitecture Day 2020を開催した。概略はジサトライッペイ氏がまとめているが、その詳細を説明したい。

米国時間の16日から開催されるHotChips 32で、インテルはIceLake-SP(“Next Generation Intel Xeon(R) Scalable Server Processor: Icelake-SP”)とTigerLake(“Inside Tiger Lake: Intel’s Next Generation Mobile Client CPU”)、Xe GPU(“The Xe GPU Architecture”)、さらにFPGA(“Agilex Generation of Intel FPGAs”)と4つもの発表を行なう。

そのほか、17日午後には「どこかで見たおじさん」ことRaja Koduri氏による基調講演も予定されており、HotChips 32はまるでインテルの発表会かと思うほどだ。

もちろんAMDがRyzen 4000Gシリーズの詳細を公開したり、IBMのPower 10/z15、MarvellのThunder X3、さらにはXbox Series Xなども発表が予定されており、しばらくはこの連載もHotChipsシフトを組んでこれらを順に説明していくので、Tiger Lakeの話などはHotChipsの発表の後でもう少し細かく紹介するとして、まずはHotChipsでは公開されないと思われる話、つまり主にプロセスだが、これを説明しよう。

今回は10nmプロセスがメインで、7nmの話は一切出てこない。7nmは連載574回で説明した第2四半期の業績発表のなかで「この歩留まり悪化の根本的な要因となる欠陥モードは特定できており、これをもたらす根本要因の排除を行なうことそのものは可能と考えている」とインテルが説明している。そのものの対処に時間を要する状況でロードマップを出しても仕方がないだろう。

絶縁材料に新しい材料を採用

結果的に動作周波数が向上

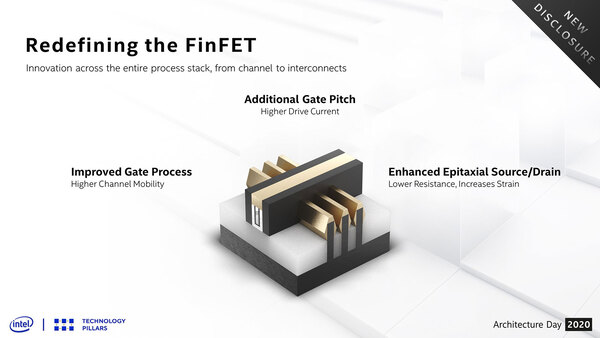

さてその10nmだ。説明上、今回のものを10nm+と表現するが、この10nm+はトランジスタに以下の改良が施された。

- ゲートの製法を改良して、より電子の移動速度を増した

- ゲートピッチをやや広げた事で、流れる電流を増やした

- ソース/ドレインのエピタキシャル成長方法を改良し、より抵抗を減らすとともに歪率を増やした

具体的な数字などは明らかにされていないため、これだけではなんとも言いにくいのだが、10nm世代のゲートピッチはもともと54nmとされていた。これはTSMCのN7やSamsungの7LPPと同じ寸法である。

ちなみにTSMCのN10は66nm、Samsungの10LPPは68nmである。インテルの10nmは他社の7nm並み、という話の理由の1つはこれなのだが、“Additional Gate Pitch”というあたりはもう少し幅広(60nm程度?)まで広げたようだ。これによって電流量を増やしたというあたりは、ゲートの幅そのものを広げたようにも思える(その結果として、ゲートピッチも広がったというあたりか?)。

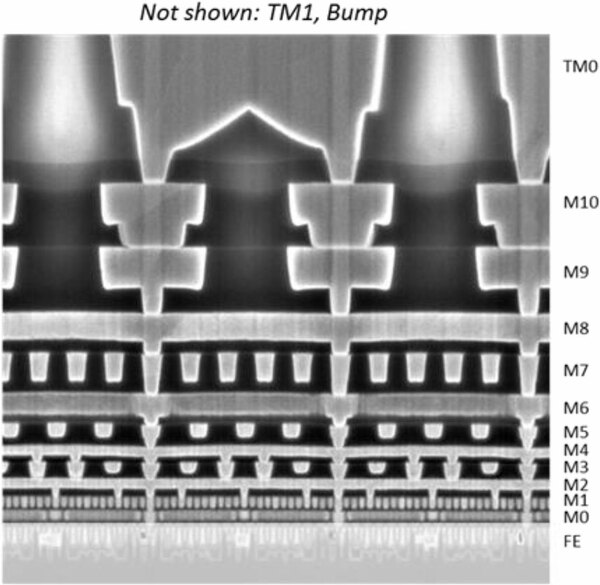

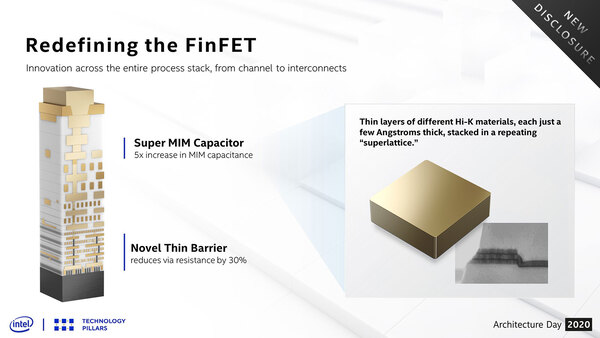

一方、配線層にも変化がある。まず配線層そのものの話。連載464回で10nmプロセスの断面写真を掲載したが、ここで言うM0~M5あたりまでの配線に関して、VIA(垂直方向の接続端子)の抵抗を30%程減らした、という話が今回明らかにされた。

これを“Novel Thin Barrier”(斬新な薄膜バリア)と表現するあたり、VIAの材料(通常はタングステン)をより抵抗の少ないものに交換したというよりは、それぞれの層の高さを削る(=高さを従来比の7割程度までにする)ことで、垂直方向の配線長を減らし、その結果として抵抗削減に成功したという表現に思える。

つまりM0~M5の層間絶縁材料に新しい有望な材料を利用したことで、高さを減じても十分に絶縁可能となったため、結果として配線抵抗を減らせたという意味だ。

これも連載464回で説明したが、昨今の先端プロセスの場合、動作周波数を決めているのはトランジスタというよりは配線遅延であり、配線抵抗を減らすことでこの配線遅延の影響を緩和できるという話である。

M0~M5あたりまでは回路配線に思いっきり利用する範囲だから、ここの垂直方向の抵抗(と配線距離そのもの)を減らすことで、結果的により動作周波数を上げやすくなったものとみられる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ