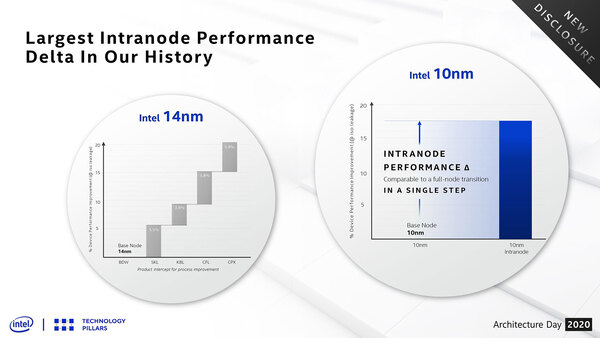

新しい10nm+は10nmと比較して

17~18%の性能改善

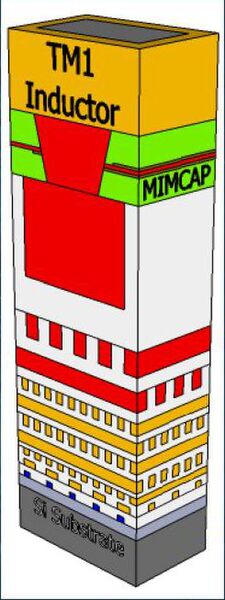

もう1つのSuper MIM(Metal-Insulator-Metal) Capacitorは要するにコンデンサーのことである。連載483回に14nmの例を示したが、配線層の一番上にInductor(いわゆるコイル)、その下の層にコンデンサーが積層されているのがおわかりだろう。

このコンデンサーは、電源用のバイパスコンデンサーとは異なる(電源用のパスコンには容量が足りない)が、デジタル回路はともかくアナログ回路ではコンデンサーが必要になってくる。

これはSoCを構築する際には絶対必要な要素であるが、この容量を5倍にしたという話である。ちなみにコンデンサの容量Cは以下の公式で決まる。

C=ε×S÷d(ε:2枚の電極板の間の誘電率 S:電極版の面積 d:電極板の間隔)

例えば電極板の面積を広げたり間隔を狭めるなどすれば容量を増やしやすい。ただ単体部品はともかく、10nmなり14nmなりのプロセスに組み込む場合は、こうした機械的な寸法はいじりにくい。説明によれば、新しいHi-K材料を使うことでこれを実現したとしている。

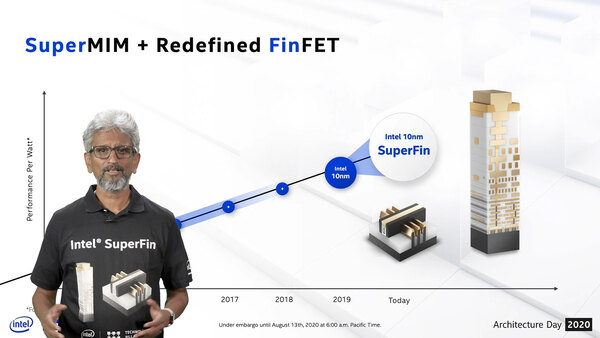

この2つの併用によって、新しい10nm+は10nmと比較して17~18%の性能改善を果たしたというのがインテルの説明である。

インテルによれば14nm世代も細かく性能改善をしていたそうで、その結果として最新のものはBroadwell比で20%ほど性能が向上したとするが、CPXというのはCooper Lakeのことだろうか?(Comet Lakeとも思えない)

ちなみにこの縦軸は「リーク電流一定の場合のパフォーマンス(≒スイッチング速度)」であり、同じ消費電力ならば17~18%高速に動作する、という意味と考えていいだろう。

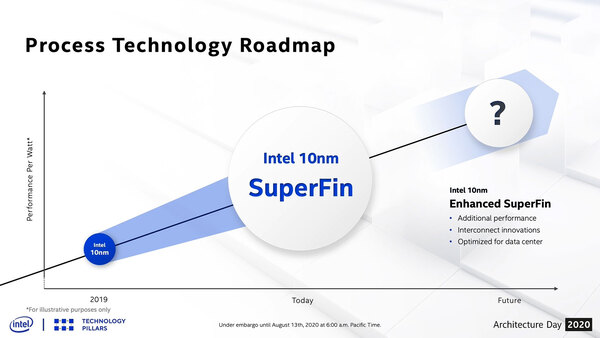

この新しい10nm+に相当するプロセスを、インテルは“10nm SuperFin”と称することにしたようだ。

というのはその次、10nm++に相当するものは“Enhanced SuperFin”という表現になっているからだ。

ただし、このEnhanced SuperFinに関してはデータセンター、それもPonte VecchioなどのGPU向けに留まる可能性も出てきた(将来のXeonがどうなるのかは不明)。まずは10nm SuperFinをきちんと量産するのが先という話であろう。

さてその10nm SuperFinを利用するのがTiger Lakeであることも今回公開されたが、Tiger Lakeは冒頭にも書いたようにHot Chipsで詳細が出てくるので来週送りにさせていただくとして、プロセスに関係する部分を少しだけ説明しよう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ