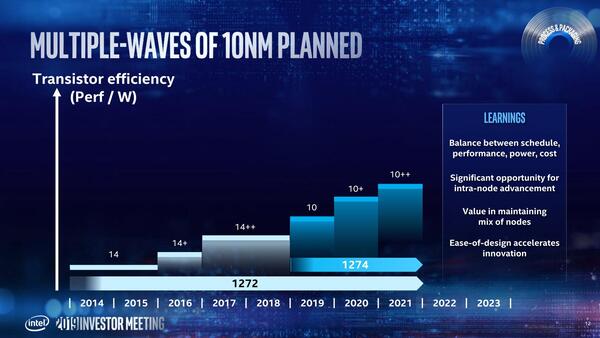

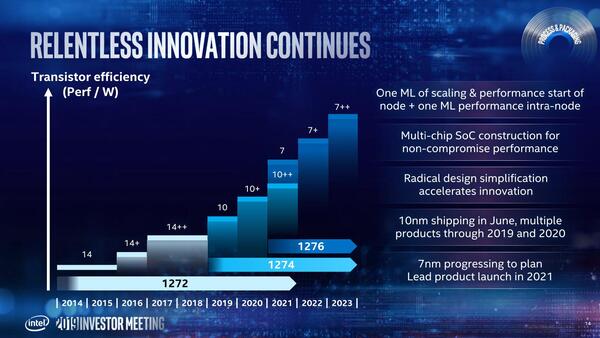

2019年は10nm、2020年は10+、2021年は10++

さらに2021年には7nmも立ち上がる

さて、ここからが今後の話である。今年は10nmであるが、2020年は10+、2021年は10++、14nmと同じようにプロセスの改善を施していくことがまず明らかにされた。

もともと10nmがスケジュール優先、つまりPPA(Power/Performance/Area=Cost)の最適化をそこそこにして、それよりも確実に出荷できることを優先したと思われるので、当然まだPPAの最適化の余地が残されている。これを2年かけて実施する予定と思われる。

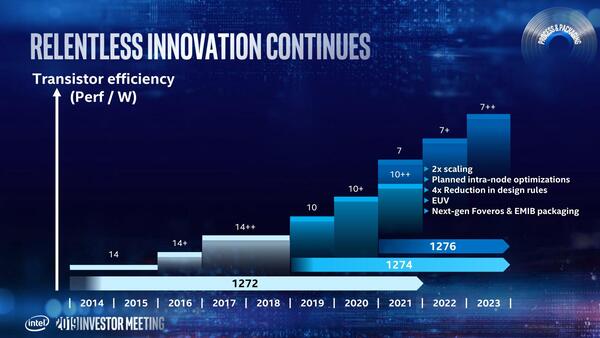

その2021年には7nmが立ち上がる。こちらも7nmに加えて7+/7++という2つの中間ノードが予定されていることが今回明らかにされた。こちらはEUV(極端紫外線)を使う最初のプロセスであり、トランジスタ密度は10nmの2倍になるとされる。この世代ではまた、高密度実装技術のEMIB(Embedded Multi-die Interconnect Bridge)とFoverosの新バージョンも投入されるとしているが、この詳細は不明だ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 - この連載の一覧へ