前回に続きCRI(Cray Research, Inc.)の話である。CRAY-1の完成後、シーモア・クレイはCRAY-2の設計に着手する。

CRAY-2

これに先立ちクレイはCRIを辞任すると同時に、コンサルタントとして同社と契約する。また、クレイは本社から離れた場所での作業を望み、これを受けて同社はコロラド州のボルダーにCRAY Labsを開設。CRAY-2の開発はここで行なわれた。

CRAY-2の目標は

CRAY-1の10倍の性能

CRAY-2の設計目標は、CRAY-1の10倍の性能だった。世代毎に10倍というのはもはやクレの信念に近いのかもしれない。では、どうやってそれを実現するかが次の問題である。

クレイの設計目標は単純だった。実行ユニット数を増やし、動作周波数を上げ、かつ信号遅延を減らせばいい。

CDC 8600はまさしくこの好例で、CDC 7600を小型化することで信号遅延を削減し、さらに実行ユニット数を増やすため4台分まとめて動作させて、CDC 7600から大きく性能を引き上げようと目論んだわけだが、うまく行かなかったことは連載273回ですでに述べた通りだ。何がまずかったのかのかは後に回すとして、CRAY-2の話に戻ろう。

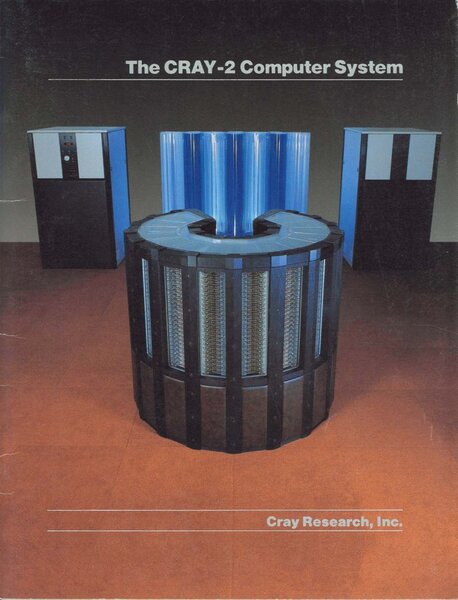

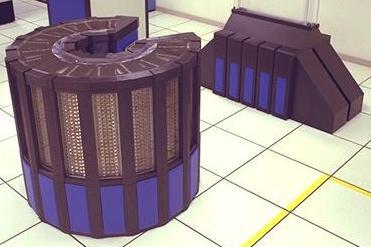

CRAY-2は最大で4プロセッサー構成が予定されていた。厳密には「4バックグラウンド・プロセッサー」構成である。下の画像がその4プロセッサー構成だ。

1つのフォアグラウンド・プロセッサーから最大4本の高速チャネルが出て、ここにディスクドライブやフロントエンド(いわゆる通信装置類)やテープドライブがぶら下る。

そしてフォアグラウンド・プロセッサーとコモンメモリーの間には、4つのバックグラウンド・プロセッサーがぶら下るという構成である。

強いていえば、このフォアグラウンド・プロセッサーというのは最近のCPUでいう所の、In-orderで駆動されるフォアグラウンド(キャッシュのプリフェッチ~デコードとスケジューラーまで)に相当し、バックグラウンド・プロセッサーはOut-of-orderで駆動されるバックグラウンド(実行ユニット~ライトバックまで)に相当するといったところだろうか。

もちろんCRAY-2の方がもっと粒度が大きいし、フォアグラウンド・プロセッサーは他にもシステム管理などの作業も担っているので、厳密には違うのだが。

このバックグラウンド・プロセッサーの構造が下の画像である。CRAY-1の内部構造と非常に良く似ていることがわかる。

といっても、多少は異なっている。まずアドレスサイズは32bitに拡張されている。またアドレス(A)レジスター/ベクトルレジスター(V)/スカラーレジスター(S)の数は同じだが、アドレスセーブ(B)とスカラーセーブ(T)のレジスターは省かれた。

そしてベクトルユニットはLogicalとIntegerの2つになったりと細かく変更があるのは、おそらくはCRAY-1での使われ方を見ながら、ある程度最適化したものと思われる。

搭載メモリー量とメモリー種別はモデルによって違いがあり、以下のようになっている。

| CRAY-2の搭載メモリー量とメモリー種別 | ||||

|---|---|---|---|---|

| Background Processor | 2 | 2 | 4 | 4 |

| SRAM(64bit words) | 64M | 128M | 128M | N/A |

| DRAM(64bit words) | N/A | N/A | N/A | 256M |

| Disk Storage | 4-18 | 4-18 | 4-36 | 4-36 |

| 6 or 12MB/sec channel | 2-8 | 2-8 | 4-16 | 4-16 |

| Magnetic Tape channel | 0-8 | 0-8 | 0-16 | 0-16 |

| 100MB/sec channel | 0-4 | 0-4 | 0-8 | 0-8 |

ハイエンドはDRAMで2GB(256Mwords@64bit)ものメモリーを搭載するという怪物で、これは大きなデータ量を必要とする計算向けである。

逆にSRAMベースの1GB(128Mwords@64bit)モデルは高性能演算向けという位置づけで、同社によればDRAMに比べて15~25%高いスループットが実現できるとしていた。

ちなみにサイクルタイムそのものは4.1ナノ秒(243.9MHz)まで短縮されており、この結果ピーク性能は1つのバックグラウンド・プロセッサーあたり487.8MFLOPS。4プロセッサー構成では1.95GFLOPSに達する。

CRAY-1のピーク性能160MFLOPSに過ぎないから、10倍以上の高速化となる。実際同社のカタログでは、演算性能はCRAY-1の6~12倍に達すると説明されている。

→次のページヘ続く (立体積層で配線遅延を解決)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ